# Design Exercise: Distributing 1080p Video in Large Scale Sunrise Systems LED Signs

System architecture and design for upper level video flow control to enable rapid manufacture of high resolution (1080p) LED video signs from existing Sunrise modules.

|     | Contents                         |

|-----|----------------------------------|

| 1.  | Problem Statement                |

| 1.1 | Top Level Constraints2           |

| 1.2 | Timing2                          |

| 1.3 | Existing Modules3                |

| 1.4 | Acknowledgments4                 |

| 1.5 | Video Distribution5              |

| 2.  | System Design11                  |

| 2.1 | System Control PCB12             |

| 2.2 | Production VCTL PCB              |

| 2.3 | VCTL Test & Commission19         |

| 2.4 | Module PCB20                     |

| 2.5 | Production VMOD PCB26            |

| 2.6 | VMOD Test & Commission28         |

| 2.7 | Sign Commissioning & Maintenance |

| 3.  | Software Walk-Through30          |

| 3.1 | Protocols                        |

| 3.2 | VMOD Software                    |

| 3.3 | VCTL Software41                  |

| 4.  | Test Plan49                      |

| 4.1 | Control PCB49                    |

| 4.2 | Module PCB54                     |

| 4.3 | Production Software55            |

| 4.4 | Production Hardware55            |

| 5.  | Hardware and Schematics56        |

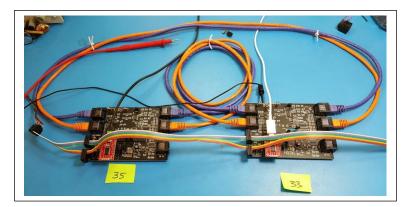

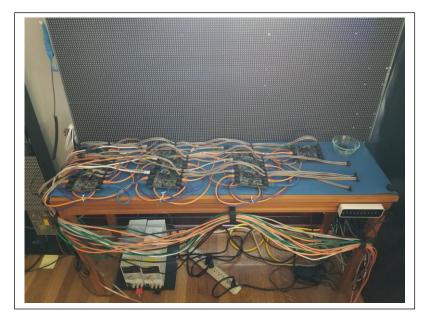

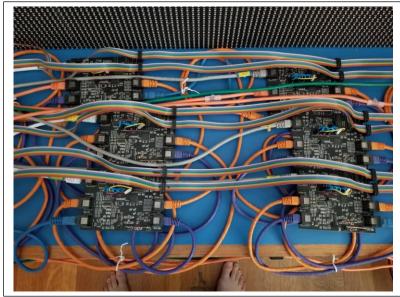

| 5.1 | Photos56                         |

| 5.2 | Schematics58                     |

| 6.  | Revision History77               |

# 1. Problem Statement

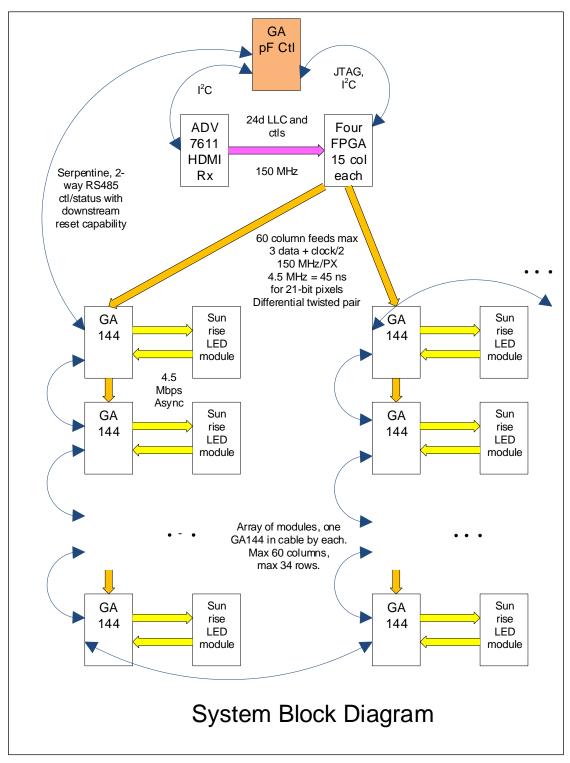

In Summer of 2015, Sunrise Systems, Inc. funded GreenArrays to design a simple, practical video distribution system that would enable Sunrise to build very large LED signs, running full 1080p video from an HDMI source, from it existing LED sign modules. Each module had an array of LED pixels with pitches typically 7.62mm; each module was controlled by an ARM processor receiving commands on an RS485 compatible serial interface running 4.5 Megabit asynchronous communications. A full sign might have on the order of 2,000 modules.

Sunrise has kindly given us permission to discuss the resulting design in this App Note. As it turned out, Sunrise concluded that its customers for such signs did not actually require the versatility of displaying real time 1080P video from an arbitrary source, so the design was never produced.

#### Referenced documents:

http://www.analog.com/media/en/technical-documentation/data-sheets/ADV7800.pdf

https://ez.analog.com/servlet/JiveServlet/download/1548-7-7431/ADV7800%20Manuals.zip

http://www.analog.com/en/search.html?q=ADV7610BBCZ-P-RL

HDMI Specification 1.3a for High Definition Multimedia Interface

CEA-861-D for EDID 1.3 structure specification and CEA Extension Version 3-

This section outlines our thought process in understanding and addressing this problem.

# 1.1 Top Level Constraints

The sign will be built to a specified display resolution corresponding with a standard video format.

- The target is 1080p; no larger formats are contemplated.

- A given system will be set up for a single video format and all input will be in that format. 1080p is the benchmark.

- No video format conversion is contemplated.

- The display may be built to a smaller size than full 1080p by using a smaller array of modules. When this is done the system must be configurable to "window" a prescribed rectangle (of the same size as the physical display in pixels) from the incoming video image onto the display. So a nonzero X,Y origin must be supported as must a rectangle size X,Y less than or equal to the full size of the incoming video frame.

- Pixel data are in 24-bit RGB format. Sunrise believes that 21 bits may be enough and has stated that 18 bits is not acceptable.

The sign will be built of the following components:

- An incoming video chip. The Analog Devices ADV7800 is postulated as the candidate.

- An array of Sunrise Systems LED sign modules. The communication protocol used to deliver video to these

modules may be changed to facilitate a clean system design but no other fundamental changes are to be

made in the modules unless they produce a significant architectural advantage.

- A video signal processing and routing system will connect the incoming video chip with the array of modules. This study is primarily concerned with the design and implementation of this subsystem.

- We will probably need to provide a processor to manage the sign as a whole, programming the incoming video chip, supporting test modes, and reporting status to an upstream system.

# 1.2 Timing

The project had an aggressive schedule for design and prototyping.

# 1.3 Existing Modules

This section summarizes the specification of the existing functional modules.

#### 1.3.1 Incoming Video Chip

An example of a suitable chip is the Analog Devices ADV7800 which converts standard video formats on standard media to a (24-bit) RGB parallel interface when suitably programmed.

Product page: <a href="http://www.analog.com/en/products/audio-video/video-decoders/adv7800.html">http://www.analog.com/en/products/audio-video/video-decoders/adv7800.html</a>

Data sheet: <a href="http://www.analog.com/media/en/technical-documentation/data-sheets/ADV7800.pdf">http://www.analog.com/media/en/technical-documentation/data-sheets/ADV7800.pdf</a>

HW/SW Design Manuals: <a href="https://ez.analog.com/servlet/JiveServlet/JiveServlet/download/1548-7-7431/ADV7800%20Manuals.zip">https://ez.analog.com/servlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/JiveServlet/J

VDD is 1.8V for digital supply, nominally 3.3V for analog and apparently for digital I/O, 2.5V for DDR SDRAM. Further investigation needed, level shifting apparently necessary to drive 1.8v cleanly

Another possibility, costing about 1/3 as much, is the AD 7610. Data may be retrieved from this URL:

http://www.analog.com/en/search.html?q=ADV7610BBCZ-P-RL

Programming is done over one or two I<sup>2</sup>C ports. It does not seem to support video format conversion nor windowing.

Output pixel rate will be somewhere between 124.416 MHz (8.04 ns), the *average* rate of 1080p at 60 Hz, and 150 MHz (6.66 ns), the maximum rate specified by the chip. The pixel clock per VESA 12p is 148.5 MHz (6.7 ns); that video format allows for 1125 line times per frame and 2200 pixel times per line, hence the difference between average rate and the sustained rate during each horizontal line. Our calculations assume the chip's max rate of 150 MHz for TPIX and FPIX as being prudent.

Output digital signal drive needs further investigation and is apparently programmable. The normal N drive appears to be on the order of 3.2 mA while the P drive seems to be only 400  $\mu$ A, which might be appropriate for I<sup>2</sup>C which has external pull-up resistors but not for the parallel pixel data out which certainly should not be single ended.

#### 1.3.2 Sunrise LED Modules

As of 14 Sep 2015, the modules Sunrise contemplates using are in several pixel formats and pitches to achieve desired sign dimensions and pixel resolution. No module would be wider than 40 pixels (this upper limit is architecturally important.) LED control is mulltiplexed 2, 4 or 10 ways, but that is not relevant outside the module:

| Pixels PX,PY | Pitch  | mm                 | Inches           | Modules @ 1080p<br>MX, MY |

|--------------|--------|--------------------|------------------|---------------------------|

| 32x32        | 3.75mm | 120 <sup>2</sup>   | 4.7 <sup>2</sup> | 60x34 (2040)              |

| 24x24        | 6.35mm | 152.4 <sup>2</sup> | 6 <sup>2</sup>   | 80X45 (3600)              |

| 30x16/24/32  | 7.62mm | 228.6 in x         | 9 x various      | 64x68/45/34               |

| 40x16/24/32  | 7.62mm | 304.8 in x         | 12 x various     | 48x68/45/34               |

| 32x24        | 12.7mm | 406.4x304.8        | 16x12            | 60x34 (1632)              |

We are assuming that the maximum practical sign array is 60x34 (2,040) modules. The X dimension (60) is architecturally important.

Each module has an ARM processor with three *unidirectional* RS422 interfaces presently doing async at 4.25 or 0.875 Mbit/s but these will be re-purposed. We may change the ARM code (written in Forth) to facilitate protocol changes that would make this system more tractable, and if necessary will arrange for bidirectional RS422. Multiple modules are presently handled by daisy chaining the high speed interface (data, one in & one out) and discretely wiring each module's lower speed control channel. We have schematics and source code listings for existing modules.

#### 1.3.2.1 Serial Communications

The ARM processor has three active UARTs. All external connections are made on 8-pin connectors J6 and J7. These connections are RS422/486 driven by AM26LS31 and received by AM26LS32A, with  $V_{DD}$  set at 5V. All modules' ARM chips use a 12.000 MHz crystal controlling internal clock of six times that frequency (to 72.000 MHz) for computer and peripheral clocks. The UARTs according to the code are set by divisors against 1/16 this frequency, or 4.500 MHz. Baud rates described in the code are NOT running at the frequencies stated but rather at the values shown below. All UARTS are set with Line Control Register (LCR) of x03 giving 8 data bits, 1SB, no parity. We do not know yet how tolerant this UART is of inaccurate baud rates.

UART1 (control) receives signal from J7.7/8 and the modules can be configured to repeat this signal out J6.7/8 without any processing, and with or without buffering. This input is stiffened by 1k/1k/1k voltage dividers between  $V_{DD}$  and ground, unlike the other inputs. This UART is normally configured in the code for 875 kbps, however that gives a divisor of 5.125 of which 5 is used so the actual frequency appears to be 900.0 kbps.

UART2 can receive signal from RX-L (J7.1/2) and can transmit on TX-R (J6.1/2). UART3 can receive from RX-R (J6.3/6) and can transmit on TX-L (J7.3/6). These inputs have  $100\Omega$  parallel termination. The code is configured for a baud rate of 4.375 Mbps, however that gives a divisor of 1.125 so the actual frequency appears to be 4.500 Mbps.

Therefore it appears we have the resources necessary to establish bidirectional communication with the module if the module's code is altered for this application and if we wish to do so.

# 1.4 Acknowledgments

This work, as noted earlier, was funded by Sunrise Systems. In addition, Sunrise provided LED modules along with their source code and documentation, and fabricated the prototype PCBs.

We licensed SwiftX™ from FORTH, Inc. to compile and flash changes for the Sunrise modules' code.

System design was done primarily by Greg Bailey and Mark Smeder. F18 programming was done by Greg Bailey and Charley Shattuck. Hardware design was done by Mark Smeder, Greg Bailey and Warren Sarkison, with Glenn Sanderson's assistance in solving some signal quality problems on the VCTL prototype. ARM programming was done by Dean Sanderson. FPGA design was done by James Bowman. Prototype assembly was done by Mark Smeder and Greg Bailey. PCB rework was done by Greg Bailey, Mark Smeder and Matt Williams of Sunrise. Greg Bailey did the study and analyses of the ADV7611 chip and of the JTAG programming of FPGAs. Documentation was produced by Greg Bailey. At various points in this project, all of the above team members contributed to each other's activities, and in addition Eric Harrington and Steve Budak of Sunrise contributed insights and answered questions about the problem statement, parts selection and manufacturing issues. Finally, Chuck Moore contributed ideas during the initial stages and served helped us understand wierd things as they came up.

Existing GreenArrays software components, created by our entire team, were used in this project, as was the GA144 polyFORTH® system whose implementation was done by GreenArrays and whose architecture was kindly contributed by FORTH, Inc. This is the first project in which the work done by Stefan Mauerhofer on excitation of high frequency crystals was depended upon, both for the asynchronous communications channels and for the Ethernet interface.

#### 1.5 Video Distribution

The central problem is to capture and distribute the relevant pixel data to each of the display modules with minimal complexity, wiring problems, and wasted energy. (Some energy saving measures may not be desirable. For example, not propagating data thru a daisy chain any farther than it is needed would tend to add a power consumption signal component looking like a 60 Hz saw-tooth.)

Sunrise, and we, are thinking in terms of attaching a GA144 to each module within the cable harness. This would allow each of the GA144s to buffer and move one module's worth of pixel data into the ARM without stress in storage (40\*32 or 1280 pixels max, 3840 bytes; This could readily be stored in 60 nodes at one byte per word of local RAM, or 30 nodes at 2 bytes per word) or time (16 ms frame time to move 3840 bytes, on the order of 1.920 Mbit/s).

Given this, everything then depends on getting each module's data into its dedicated GA144 once per frame, using a small fraction of a frame time so that we *do* have most of a frame time to talk with the ARM. To accomplish that we must split the incoming video into multiple streams, each at a significantly longer pixel period than TPIX.

#### 1.5.1 General Strategies

We considered running all pixels down the left side of the display, buffering each module row at one place on the left side and then propagating the data across the row much as we'd discussed for direct LED drive. The vertical bus would be running 24 bits wide at TPIX, presumably daisy chained between devices, but the transmission across each module row could be done on the order of TPIX\*MY. This is still 226 ns per pixel (4.41 Mpix/s or 105.9 Mbit/s) and that transmission rate would require a parallel interface of some width going across each module row. Ignoring the logical and electrical problems that come with this high speed parallel transmission, this would also require buffering one module row (32 pixel rows) of data at each of 34 places on the left side. 32 pixel rows is 32x1920 or 61440 pixels, 184320 bytes of buffered data in something (FPGA) out to the left of each module row. That's perhaps 34 expensive FPGAs, one high speed bus down the height of the sign and 34 high speed buses across the module rows. While obvious this strategy has some serious defects and we have concluded it is not a good way to go.

A less obvious strategy is to select, in each video scan line, the pixels destined for each column of modules and run the data down those columns basically in parallel. Unlike the left side, there is no requirement for large buffers but only the PX pixels in a FIFO for each column. The data rate is better than any horizontal strategy because there are fewer data to be sent down a column of modules than across a row of them; each pixel going down a column needs to be disposed of in time on the order of TPIX\*MX which is larger than TPIX\*MY. MX of 48 gives worst case 1080p timing:

| Pixels <b>PX,PY</b> | мх | Pixel time<br>TPIX*MX ns | Pixel Freq<br>Mpix/s | Bit freq<br>Mbit/s | Bit time<br>ns |

|---------------------|----|--------------------------|----------------------|--------------------|----------------|

| 32x32               | 60 | 399.60                   | 2.5                  | 60.1               | 16.65          |

| 40x32               | 48 | 319.68                   | 3.13                 | 75.08              | 13.32          |

The pixel clock per VESA 12p is 148.5 MHz (6.7 ns) however that video format allows for 1125 line times and 2200 pixel times per line. The extra vertical lines do not help but the horizontal overhead does; 148.5 1920 2200 \*/ is 129.6 MHz (7.7 ns), and this is the average rate we have to be able to move down the columns. TPIX and FPIX assume the higher rate of 150 MHz for prudence; to see best case numbers using our preferred strategy, multiply by 771/666 for time and 666/771 for frequency.

We have determined that these rates aren't feasible with 2-wire synchronous protocol. We will have to use a parallel daisy chain, probably of three data bits and a half-frequency clock (triggering on both edges.)

However it is implemented, though, there are two significant compelling advantages to feeding columns rather than rows; first being that there is no need for large buffers, , and second that the data rate will always be lower for normal display aspect ratios whose height is less than width in pixels. Therefore we have concluded that feeding columns of modules is the best way to go.

#### 1.5.2 Methods of Distributing to Columns

Thus far we have thought of two different ways to distribute the pixel stream to the module columns. Each has its own strengths and weaknesses; we will continue investigating both of them until all of the tradeoffs are better understood. Certainly, at least one of them should be able to do the job, if not both.

#### 1.5.2.1 The GA144 Method

The distribution is handled as an additional function of the GA144s in the top several module rows. This assumes a parallel, daisy chained bus running across each such row (12 bits plus clock). Two rows minimum are required to carry 24-bit pixels. However because we cannot keep up with TPIX this will require not just one pair of rows but probably three or four pairs to demultiplex the pixels into a slower stream for a total of MMY modules at the top of each column. Cooperation will be needed between these MMY involved modules in order to drive their data down the column (and up for data destined to the rows above each of them).

Feasibility of this method depends on several things including coordination of the demultiplexing, ability to sample reliably during the short pixel hold time, signal quality and skew control over as long a distance as 15.7 inches, and the coordination of traffic up and down the module column. It may turn out necessary to have some separate logic such as an FPGA on the left end to handle the clock stretching and the timing for demultiplexing; however if the GA144 cannot grab a pixel value from the bus driven directly by the incoming video chip some method of latching the 24 data lines three or four ways might be necessary.

Windowing in both X and Y will need to be implemented inside the GA144s, meaning that the topmost pair of rows and the leftmost column will have different code, no surprise because the rows will need different code anyway to control the up/down movement of column data.

Additionally this method gives serious failure modes; failure of a single module in the top MMY rows will affect the rest of the display to its right, and even a transient failure could easily cause gross loss of synchronization. Measures will certainly be needed to make this method robust. At this time we don't think this method is feasible with the G144A12.

#### 1.5.2.2 The FPGA Method

An alternative way to achieve the same thing involves no change in the protocol for driving the pixel data down the columns. It differs only in using a single FPGA rather than several rows of GA144s.

The FPGA would have 24-bit data and clock connected to the incoming video chip, nearby on the same PCB so that signal quality and skew are not issues. Internally, the FPGA would window the pixel stream with counters. Other counters within each scan line would drop pixels into 60 short (40x24, 960-bit) FIFOs, each of which feeds one of 60 drivers for 2-wire synchronous pixel data going down a column. The synchronous bit clock would be derived from the pixel clock so that there is no problem with overrunning these FIFOs.

Architecturally if we wound up needing more than 2-wire down the column we might not have enough GPIOs on the FPGA.

The most obvious electrical problem is adequate drive for the 60 2-wire output signals. Another unique problem for this method is that because all the distribution logic is at one point, the 2-wire signals would have to be carried a fair distance to reach the appropriate modules at the tops of the columns. If the sign control was physically placed at top center of the display, then in worst case we would have a 2-wire sync line running half the width of the sign, or 12 to 31 feet, apparently. At minimum this may require line drivers and good transmission lines for the signals.

In terms of failure modes the FPGA becomes a single point of failure for the whole sign, just like the incoming video chip and the sign control computer. Because these *are* single points of failure the assembly carrying them should most likely be available onsite as a spare, along with other major modules such as power supplies and a few display modules.

#### 1.5.3 Moving Data Down a Column

We've designed and implemented on the bench a method of moving data down a column using a GA144's parallel ports to daisy chain. The parallel data word should work at 3 data bits and might be feasible at 2 data bits; this will be investigated closely because each additional data bit added to reduce data rate increases cost per module, cost of wire, and the burden on the FPGA for pins and signal drive.

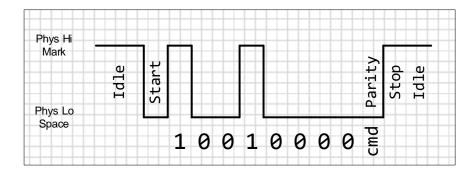

#### 1.5.3.1 Inter-GA144 Transmission Protocol

The input to each GA144 consists of n data bits and a clock. The clock is half frequency, meaning that we trigger on each of its edges. The setup time for data relative to clock edge should be positive but we believe may be zero; our method of processing the clock signal has a built-in 7.2 ns delay which gives us a "free" setup time on the data.

Within the GA144, pixel data for its module are captured based upon counting clocks. The start of a scan line and the start of a frame will be recognized by a comparatively long time-interval between clock edges, with the exact criteria to be determined. In the event that a module loses bit/word synchronization during a frame, it will ideally be able to resynch at the start of the next frame. The capture of data and its processing within the chip will have no effect at all on the transit of data through that chip and out to the next step in the daisy chain.

The output of each GA144 consists of n data bits and a clock, all driven at the same time through the parallel output port. Thus in addition to "repeating" the signals at each chip, they are automatically de-skewed.

If it is necessary to generate each of these signals as differential pairs, the GA144 can drive both wires directly from its parallel port. This will increase the delay through the chip but should not impact its bandwidth. However, some sort of differential receiver will need to be built for each line, for good common mode rejection in an environment of high power usage and thus noise on power and, probably, ground.

We have not yet measured our ability to directly receive AC coupled clock and data with reliability; this may become a question for cost control in the case of differential transmission lines. More on this below.

#### 1.5.3.2 Pipeline Implementation within GA144

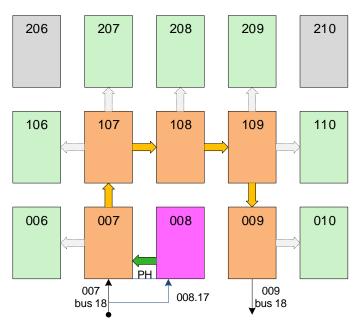

The data path for parallel reception, transmission and capture is as follows:

Parallel Data Path

Node 008 waits for a clock edge by reading **up**. Writes **io** to change state of phantom wake-up for 007, and sets to wait on other clock phase.

Node 007 reads **up+down** to capture data (and clock) lines on phantom wake-up. Writes **up+down** to send same to 107. Writes **io** to wait on other phantom wake-up phase.

Nodes 107, 108, 109 and 009 are simple wire nodes, moving data from input port to output port(s) at a typical cost of 4.85 ns. Processing may be done along the way to restore inverted pins for differential drive.

Any of the light green nodes may receive a "tap" of incoming data for internal processing. Each is *absolutely* required to be punctual, i.e. to *always* be reading by the time the next datum is available.

Basic bench code for implementing this path, with no taps active and no differential restoration, is as follows:

```

set which test to compile here

1032 list

mark 1 compile,

code 1036 1038 thru,

```

```

1034 list

- load descriptors,

stim 10705 +node 10705 /ram io /b io /a,

..3E 3B 2E 2B 3E 3B 2E 2B 2A 2B,

....10 /stack 0 /p,

10008 +node 10008 /ram 1A /io,

....16 A97 16 A97 16 A97 16 A97 16 A97,

....10 /stack up /b io /a 0 /p,

10007 +node 10007 /ram 0 /io,

....0 800 0 800 0 800 0 800 0 800 10 /stack,

....'-d-u 105 /a io /b 0 /p,

10107 +node 10107 /ram,

....down /a left /b 0 /p,

10108 +node 10107 /ram,

....left /a right /b 0 /p,

10109 +node 10107 /ram.

....right /a down /b 0 /p,

10009 +node 10107 /ram,

....down /a data /b 0 /p,

```

```

1038 list

node 008 triggers on both clock edges.,

- incoming reclaim 10008 node 0 org,

..on each edge sends same signal on phantom,

prx 00 begin begin,

..wakeups to 007/009 and inverts wake dir.,

..@b drop ! unext end,

.. nominal cycle 13ns latency 7.2ns,

02 reclaim 10007 node 0 org parallel in

node 007 reads triggered input from up/down,,

set 00 -1 1 dup push dup,

..writes value to up/down to pass it to 107,

....02 push dup push dup push dup,

..which should always be ready, and inverts,

....04 push dup push dup push push,

..wake dir. nominal cyc 16.75ns lat 5-10ns.,

run begin 06 @ ! !b unext run ;,

08 reclaim 10107 node 0 org path to out,

nodes 107-108-109-009 wire the data stream,

..from 007 to the node 9 parallel port with,

set 00 -1 1 dup push dup,

..taps done by punctual 2-port writes.,

....02 push dup push dup push dup,

..nominal cyc 13.0ns lat 5-10 ns.

....04 push dup push dup push push,

..begin begin 06 @ !b unext unext,

07 reclaim exit

```

The 2-port read by node 007 is safe because 107 will never write to it. The 2-port write is safe because the parallel port is configured for input; the instruction will write to the data register but that register does nothing. The code for node 705 is part of the test described in the next section.

Timings in nodes 008 and 007 have an additional time on the order of 10 ns in one cycle of many, when the **unext** is exhausted. This has not been measured precisely but should not give a problem at current data rates. Precise measurements will be made after we learn whether any additional processing is required within the critical path.

#### 1.5.3.3 Pipeline Testing

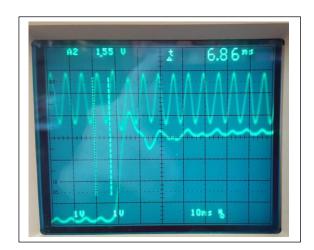

Node 705 of the target chip was programmed to produce a relatively low frequency (10 Mwords/sec) stimulus consisting of two data bits and a clock, using the code shown above, and jumpers used to carry its signals to nodes 008 and 007 as shown to the left.

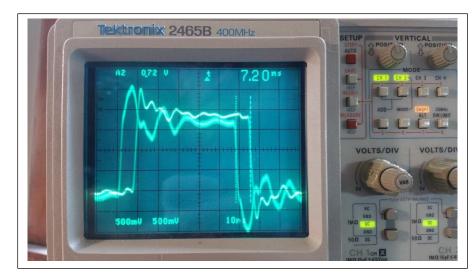

In the trace to the right, we temporarily had node 008 drive one of its output pins to show the delay between incoming clock and setting of **io** to be 7.20 ns. That is also the delay to the trigger for reading and latching node 007's parallel input.

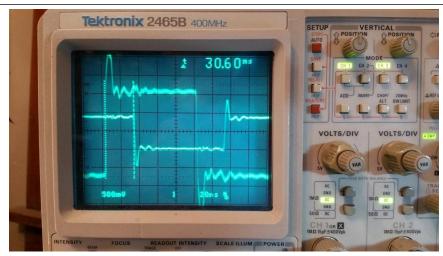

The trace to the right shows the delay between incoming clock signal at pin 008.17 and one of the outgoing data pins driven by node 009.

Subtracting 7.20 ns for the stimulus from node 008 to 007, we have a transit time of (23.40/5) or 4.68 ns per F18, which is the best case behavior of punctual wire nodes.

The system can carry a higher data rate than this delay time, of course.

#### 1.5.4 Next Steps

With a sustained pixel time of 319.68 ns down the column and worst timing (MX of 48), 2 data bits give us 26.640 ns per word for 24-bit pixels and 29.061 ns per word for 21-bit pixels. 3 data bits give us 39.960 ns for 24-bit pixels and 45.668 ns for 21-bit pixels.

# 2. System Design

Two PCBs are included: Control PCB, with HDMI video receiver, top level distribution, configuration and overall control/status duties; and Module PCB, one per Sunrise module, for video distribution down each column. This design requires some hardware difference between odd and even columns, either in the cabling or in PCB optioning, to implement the serpentine control channel. Five wire pairs go down each column: Four to distribute video and one for control/status channel.

# 2.1 System Control PCB

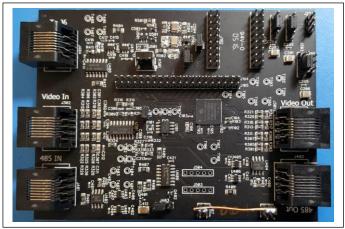

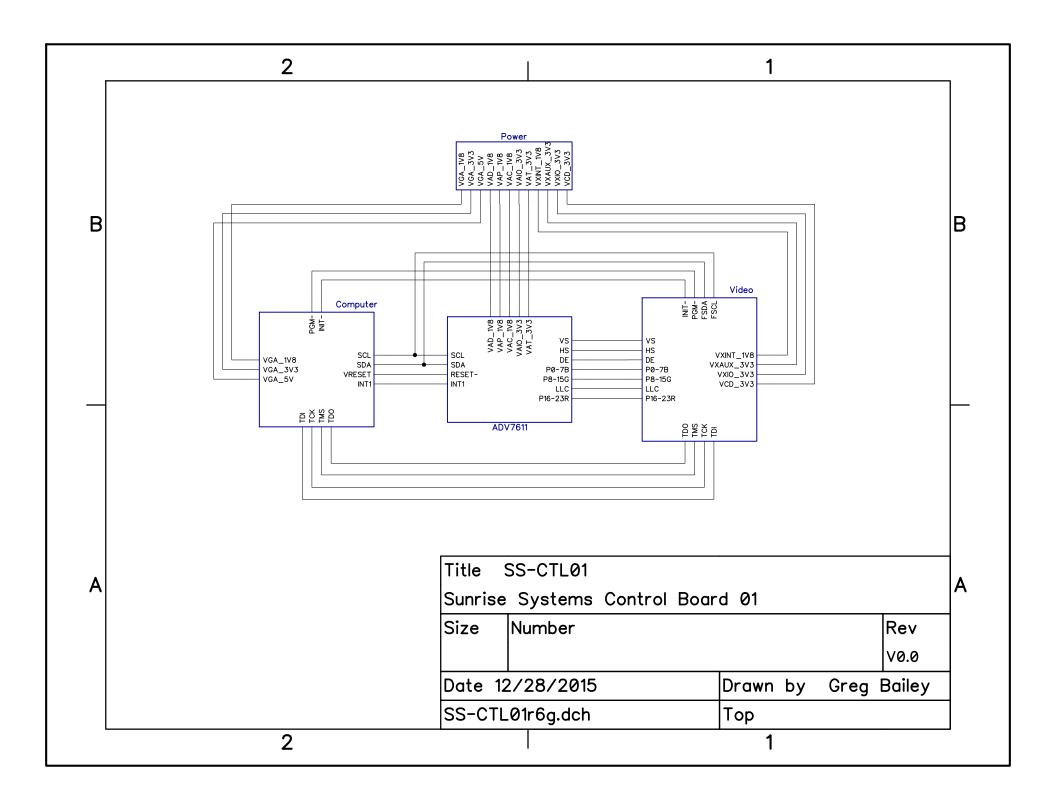

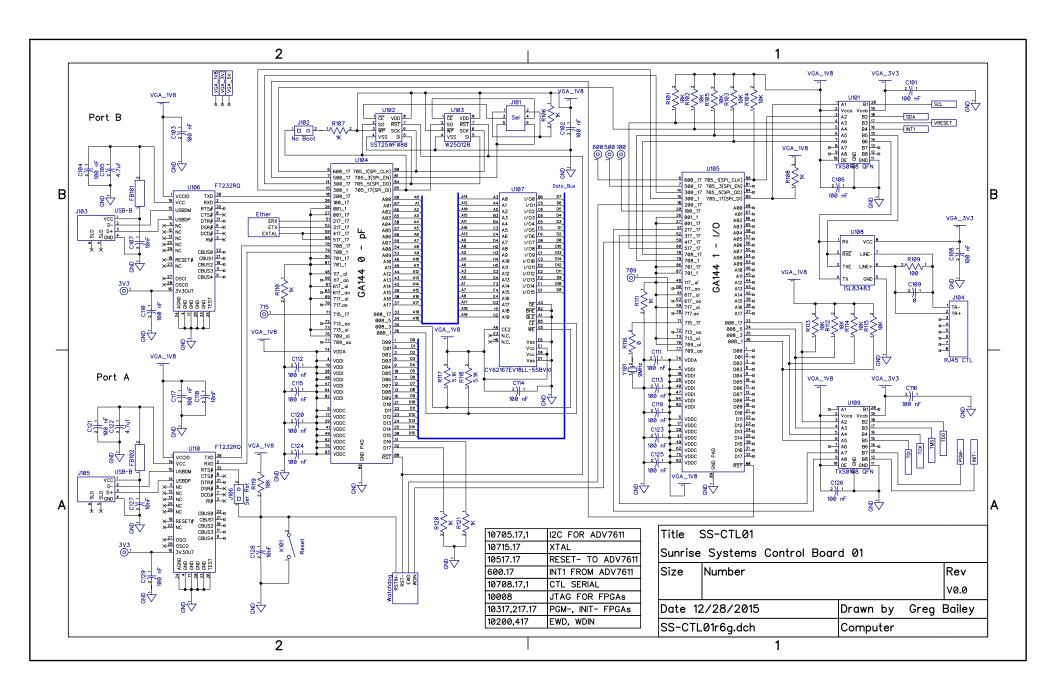

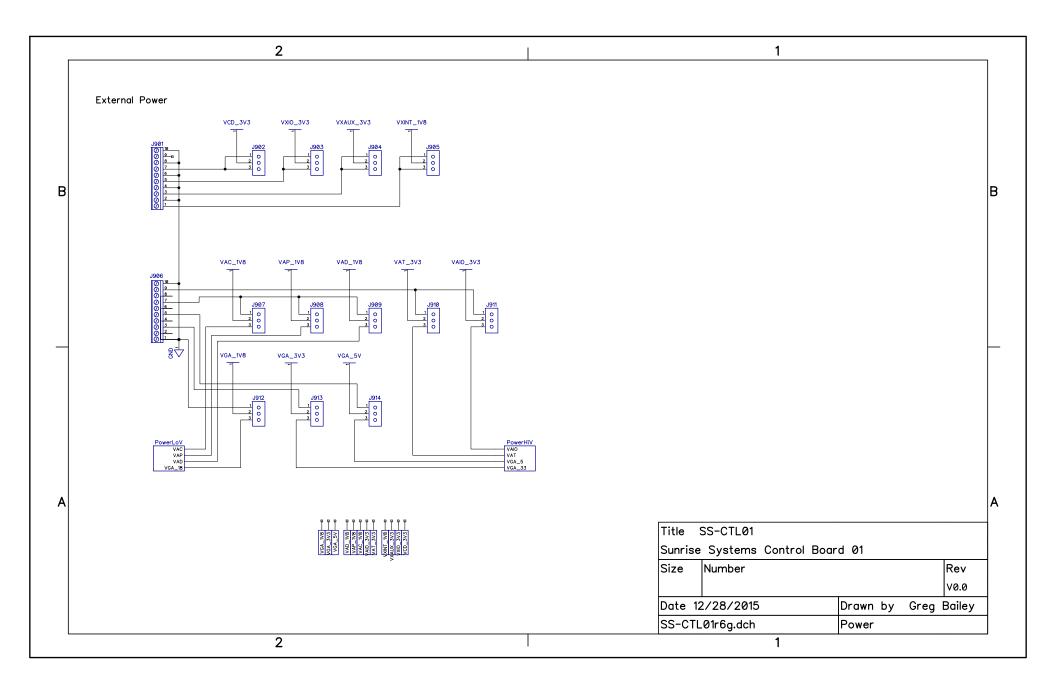

This board configures and controls the display as a whole. In this section we walk through the schematic for the board in the order of its hierarchy. Later on we will discuss the protocols implemented by software, and testing considerations.

The first page of the drawing is labeled "**Top**" and shows the highest level block diagram of the circuitry, showing the relationships between the **Computer** (two GA144s as a polyFORTH system), the **ADV7611** which receives 1080p video over an HDMI link, the **Video** section comprised of four FPGAs which decompose the 1080p signal into lower speed LVDS feeds for up to sixty columns of Sunrise LED modules, and the **Power** supply.

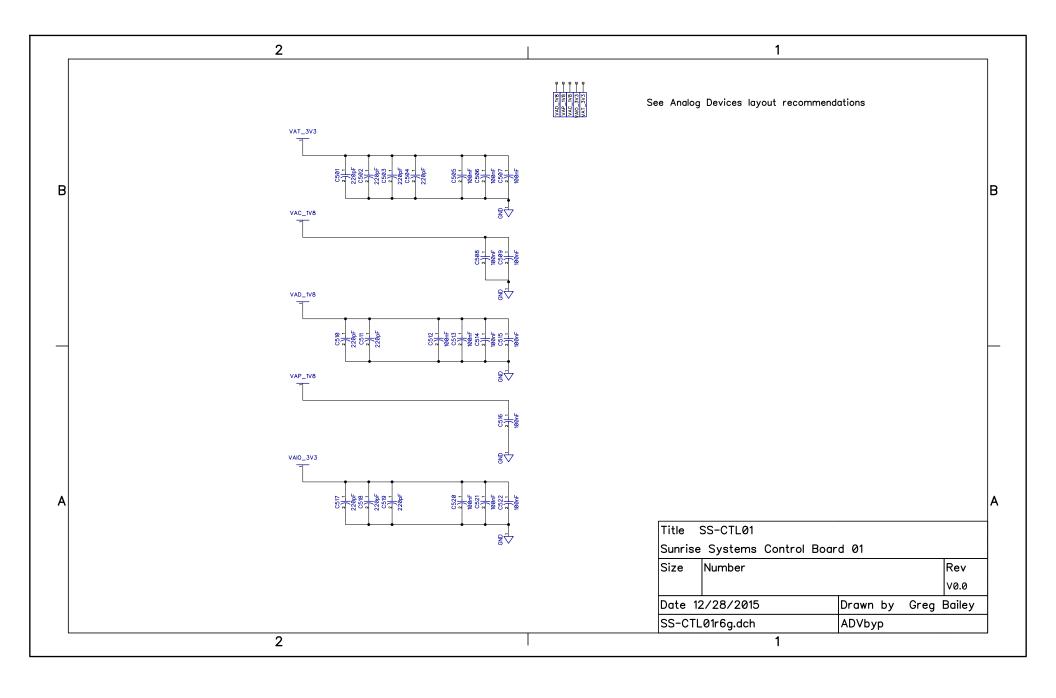

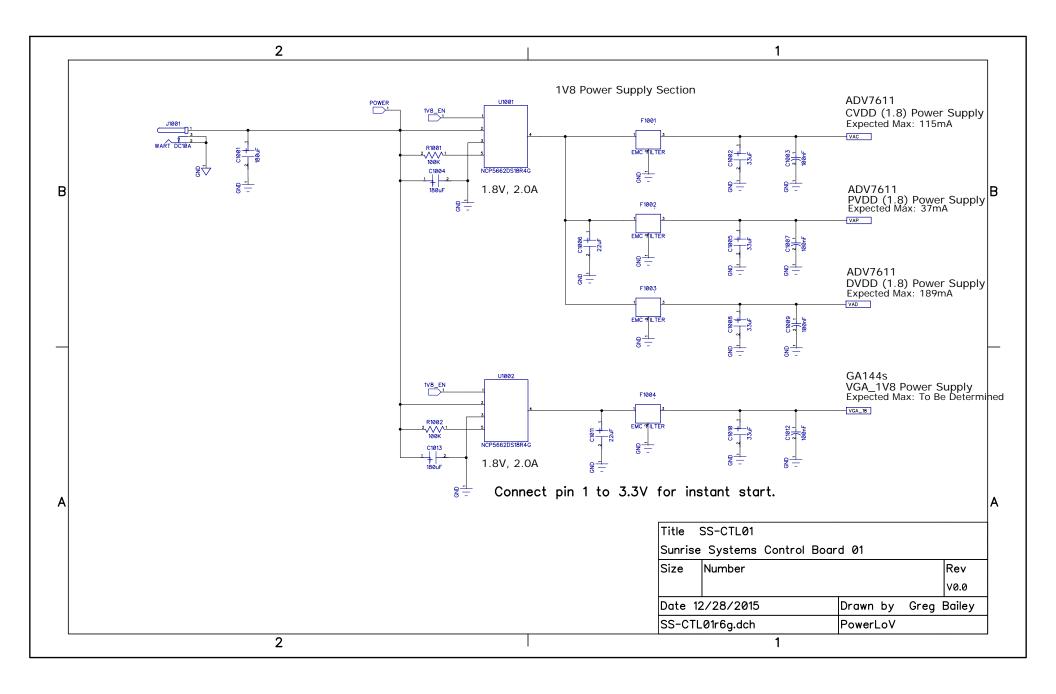

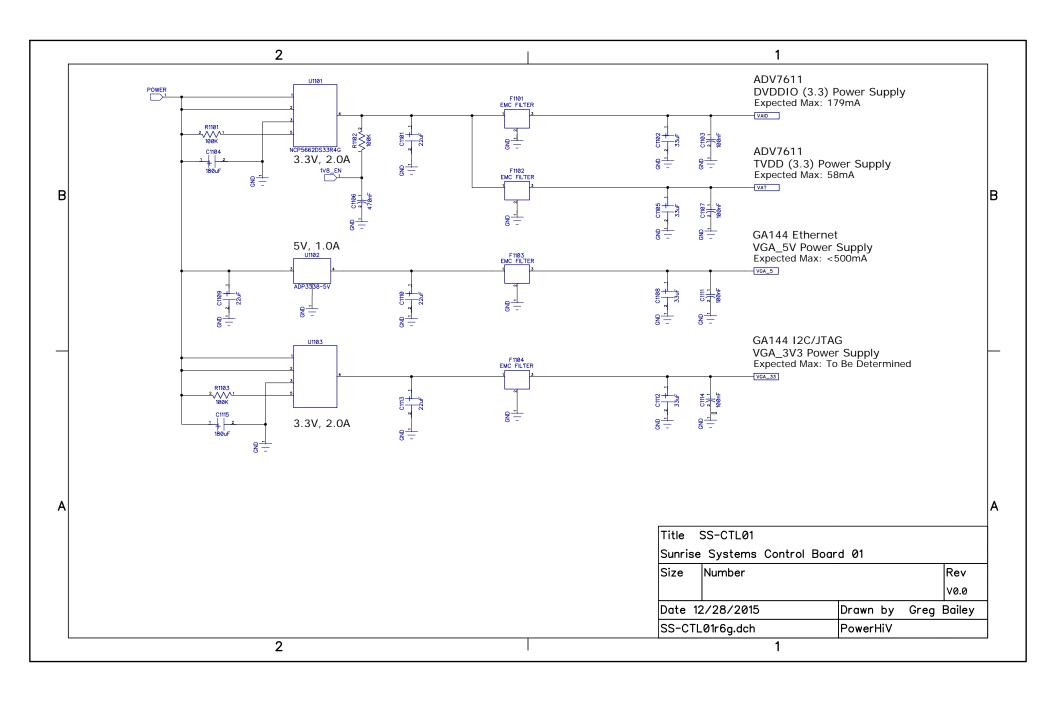

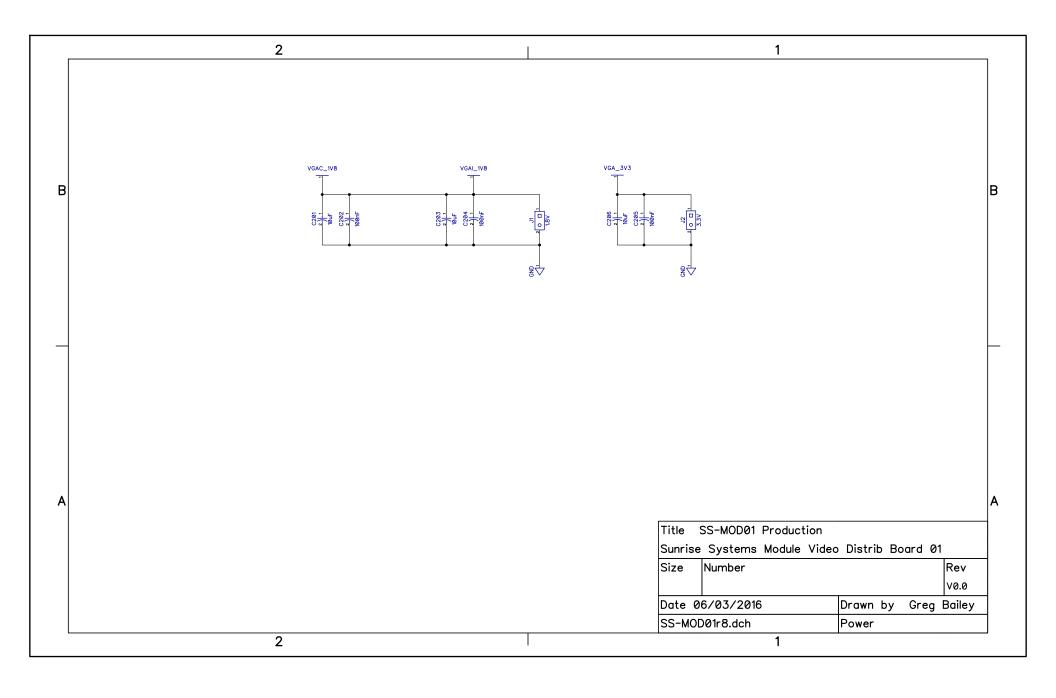

#### 2.1.1 Power Section

The main supply, powering everything but the four FPGAs and sixty 4-bit LVDS line drivers, is adapted from Analog Devices' evaluation board and comprises the last three pages of the schematic. It produces 1.8V, 3.3V and 5V from an external wall-wart. This supply uses linear regulators and will probably be simplified for production units. 3-position jumpers allow for current measurement on the 8 supply sections and also allow selection of external power from a barrier strip. These sections are:

| Name     | Voltage | Est Current | Chip/section        | Nomenclature |

|----------|---------|-------------|---------------------|--------------|

| VGA_1V8  | 1.8     | TBD         | GA144s & related    |              |

| VGA_3V3  | 3.3     | TBD         | I2C, JTAG & related |              |

| VGA_5V   | 5.0     | <500mA      | Ether transmit      |              |

| VAC_1V8  | 1.8     | 115mA       | ADV7611 Comparator  |              |

| VAP_1V8  | 1.8     | 37mA        | ADV7611 PLL         |              |

| VAD_1V8  | 1.8     | 189mA       | ADV7611 Core        |              |

| VAT_3V3  | 3.3     | 58mA        | ADV7611 Terminator  |              |

| VAIO_3V3 | 3.3     | 179mA       | ADV7611 Outputs     |              |

Because we won't know the power requirements for the FPGAs and the line drivers until the prototype is operating and we can take measurements, all power for these components is supplied externally using a barrier strip. Four supply sections each have 3 position jumpers for current measurement.

| Name      | Voltage | Est Current | Chip/section        | Nomenclature |

|-----------|---------|-------------|---------------------|--------------|

| VXINT_1V8 | 1.8     | TBD         | FPGA Internal logic |              |

| VXAUX_3V3 | 3.3     | TBD         | FPGA Aux pins       |              |

| VXIO_3V3  | 3.3     | TBD         | FPGA Outputs        |              |

| VCD_3V3   | 3.3     | TBD         | Column line drivers |              |

#### 2.1.2 Computer Section

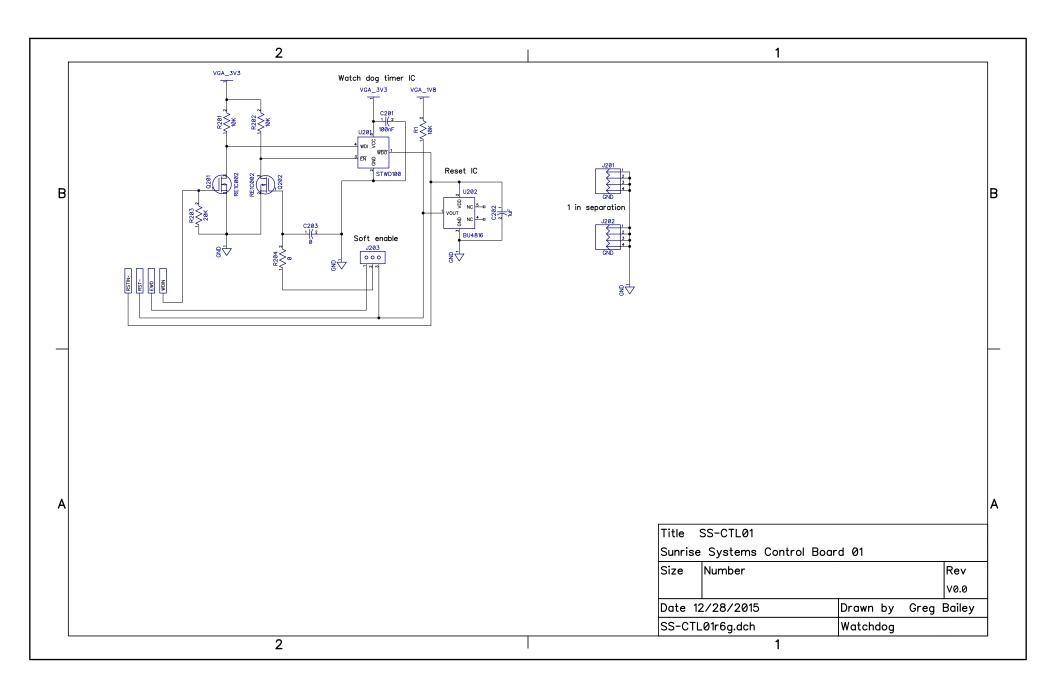

The second page of the schematic is the heart of this section. It consists of the polyFORTH system and internal system I/O, a page of Watchdog and reset circuitry, and a page of 10baseT Ethernet line interface circuitry.

#### 2.1.2.1 polyFORTH system

We have borrowed circuitry from the GreenArrays EVB001 evaluation board, including the pair of GA144s, the 2 MB SRAM, both 1MB and 16MB SPI flash for boot, operating software and FPGA programming strings, two FTDI USB to serial interfaces, the ability for USB port A to reset chip 0 and the flash, and the signals for chip 0 to boot and control chip 1. This allows the EVB001 self-test code to run on the two GA144s, omitting the SERDES tests because none of them is connected. It also allows polyFORTH to run without change.

The 10baseT Ethernet cicuitry is included, however using a 10 MHz crystal instead of a Fox oscillator. A second SPI flash, this one with 16 MB of storage, is included and jumper block substitutes it for the conventional 1 MB part. Both of these features will require code changes; Phase jitter interpolation to initially excite the crystal, and a different writing mode for the large SPI flash (the AAI write function has been deprecated.)

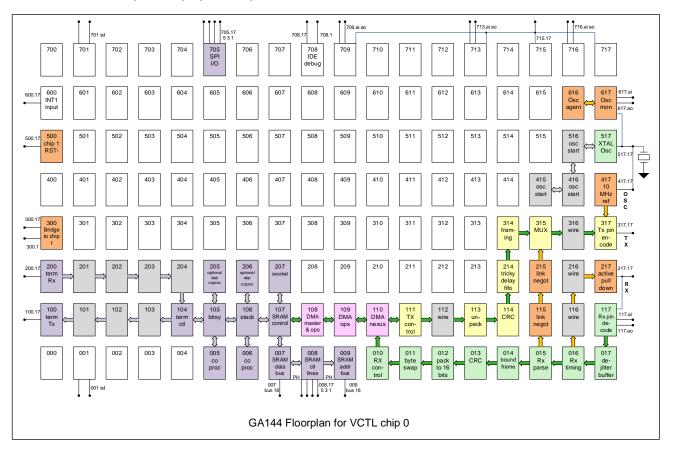

I/O pin allocation is as follows:

| Pin(s)         | Functions                       | Remarks                                 |

|----------------|---------------------------------|-----------------------------------------|

| 705.1,3,5,7    | SPI flash boot & disk           |                                         |

| 008.1,3,5,7    |                                 | Chandand of wares                       |

| 007.d0-17      | SRAM control                    | Standard pF usage.                      |

| 009.a0-17      |                                 |                                         |

| 708.1,17       | Async boot, IDE                 | Development and test/commission.        |

| 100.17, 200.17 | Async pF terminal               | Development and configuration.          |

| 500.17         | Reset to Chip 1                 | Weak PD resets chip 1.                  |

| 300.1,17       | Sync boot & bridge to chip 1    |                                         |

| 417.17, 517.17 | Ethernet 10 MHz Crystal         | Standard pF usage.                      |

| 317.17         | Ethernet Transmit               | Standard pr usage.                      |

| 217.17         | Ethernet Receive                |                                         |

| 600.17         | INT1 from ADV7611               | HDMI status changes from ADV7611        |

| 715.17         | Unused pin                      | Brought out to test point               |

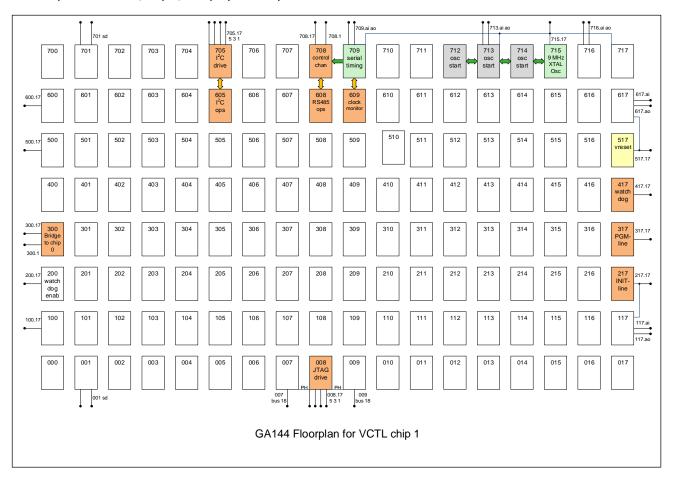

| 10300.1,17     | Sync boot & bridge from chip 0  | Standard pF usage.                      |

| 10715.17       | Xtal 9 MHz                      | For control channel baud rate           |

| 10708.1,17     | Dir (Tx) & data for ctl channel | Pulled high on reset                    |

| 10317.17       | PGM- signal for FPGAs           | Weak PD on reset                        |

| 10217.17       | INIT- signal for FPGAs          | Weak PD on reset                        |

|                |                                 | For programming FPGAs and also might be |

| 10008.1,3,5,17 | (JTAG) TDI, TCK, TMS, TDO       | usable for later comms.                 |

|                |                                 | Pulled high on reset.                   |

| 10517,17       | RESET- to ADV7611               | Pulled high on reset.                   |

| 10705.1,17     | (I2C) SDA, SCL                  | For ADV7611 and, if needed, FPGAs.      |

| 10703.1,17     | (12C) 3DA, 3CL                  | Pulled high on reset.                   |

| 10200.17       | Enable Watchdog                 | Weak PD on reset.                       |

| 10417.17       | Watchdog Retrigger              | Weak PD on reset.                       |

| 10100, 10500,  |                                 |                                         |

| 10600.17,      | Unused pins                     | Brought out to test point               |

| 10709.ao       |                                 |                                         |

After booting, polyFORTH is responsible for configuring the FPGAs and the ADV7611 HDMI video source chip. The system is capable of fully automatic and/or interactive control. Chip 1 is used for I/O expansion and is controlled by the host using Mark 2 snorkel/ganglia over the synchronous port bridge.

Jumpers in the Computer section are as follow:

| Pin(s) | Default                       | Alternate                          |

|--------|-------------------------------|------------------------------------|

| J101   | 3-5: Enables 1 MB flash.      | 1-3: Disables 1 MB flash.          |

| J101   | 2-4: Disables 16 MB flash.    | 4-6: Enables 16 MB flash.          |

| J102   | Open: Enables SPI flash boot. | 1-2: No boot.                      |

| J106   | Open: Disables USB reset.     | 1-2: Enables USB reset.            |

| J203   | 2-3: Watchdog always enabled. | 1-2: Watchdog enabled by software. |

#### 2.1.2.1.1 Lessons Learned from Prototype

Crystal footprint for Y101, still 3-pin, connects signal to center pin not end pin. Jumpered pins 2 and 3 to make this work, layout must be corrected. Also,  $0\Omega$  resistor R116 is not populated and must be shorted to allow the crystal to oscillate.

#### 2.1.2.2 Reset circuits

For the GA144 system we have a BU4816 reset chip and an STWD100NYWY3F watchdog timer. These will be evaluated for reliability in the prototype.

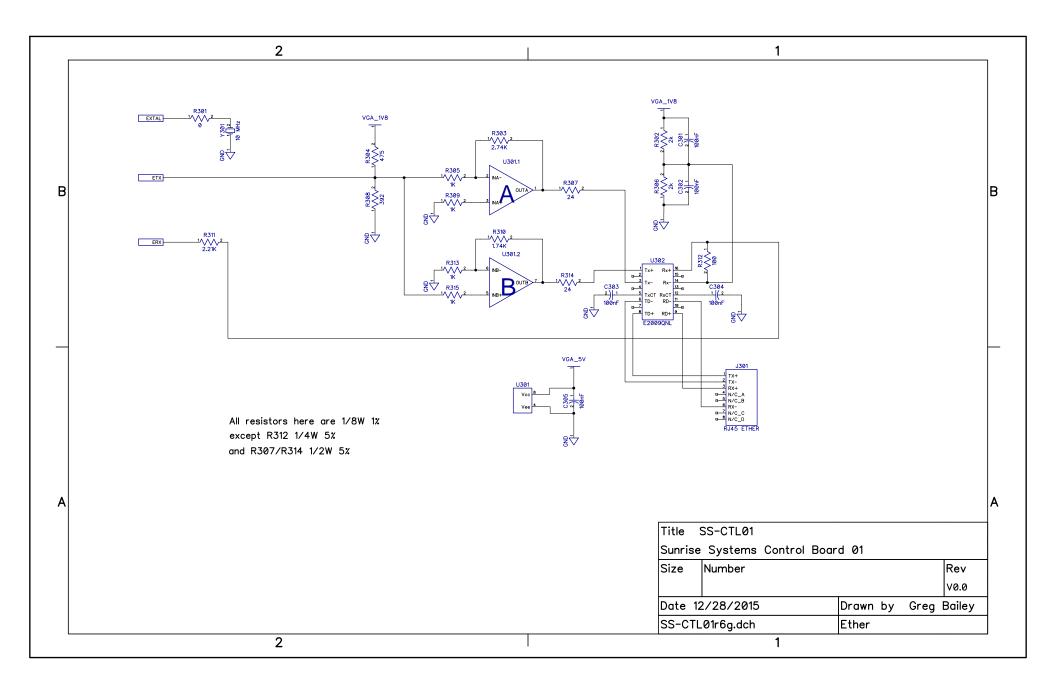

#### 2.1.2.3 Ethernet Electrical Interface

This circuit provides the electrical interface to allow three nodes with GPIO pins to connect to a 10baseT circuit. One pin runs the 10 MHz crystal which we are basically required to use as a transmit frequency reference. One acts as a transmitter using a dual op-amp to make the higher voltage differential swings required, and uses a standard transformer to interface with the Cat5 cable. The receive circuitry consists of the other half of this transformer and a series current limiting resistor to feed a GA144 pin.

#### 2.1.2.3.1 Lessons Learned from Prototype

Crystal footprint for Y301, still 3-pin, connects signal to center pin not end pin. Jumpered pins 2 and 3 to make this work, layout must be corrected. Also,  $0\Omega$  resistor R301 is not populated and must be shorted to allow the crystal to oscillate.

Our crystal oscillators will stop if disturbed with a probe on the crystal pin. They will also not start if another GA144 pin is connected to them but not set to high impedance. Evidence that a crystal is running must be obtained from a monitoring node.

#### 2.1.2.4 Interchip Communications

ADV7611 configuration is done as described in AN018.

Target node 10708 masters the 400 KHz (max) I<sup>2</sup>C bus for the HDMI chip (10708.15 is **SCL**, 10708.1 is **SDA**). 10517.15 is **RESET**- for the HDMI chip. **INT1** from HDMI is received by Host pin 600.17. All four of these pins use a TI TXS0108 level shifter to translate between 1.8V and 3.3V in an open-drain configuration.

For the FPGAs, we reset the device by pulling **PROGRAM\_B** and **INIT\_B** low. Raise **Program\_B** T<sub>PL</sub> (4 ms) before raising **INIT\_B** and raise **INIT\_B** at least T<sub>POR</sub> (40 ms) after starting the reset.

We talk to the FPGAs using six lines shifted to 3.3V by a TXS0108 open-drain level shifter. 10217.17 drives **INIT**- and 10317.17 controls **PROGRAM**- while node 10008 pins 17, 5, 3 and 1 connect with JTAG signals **TDO**, **TMS**, **TCK** and **TDI** respectively. In addition the FPGAs are part of the I<sup>2</sup>C bus until we learn whether JTAG alone is sufficient for everything we need to do. The prime reason for using open-drain level shifting is to accommodate the JTAG connector that will be used for initial debugging of the FPGA configuration.

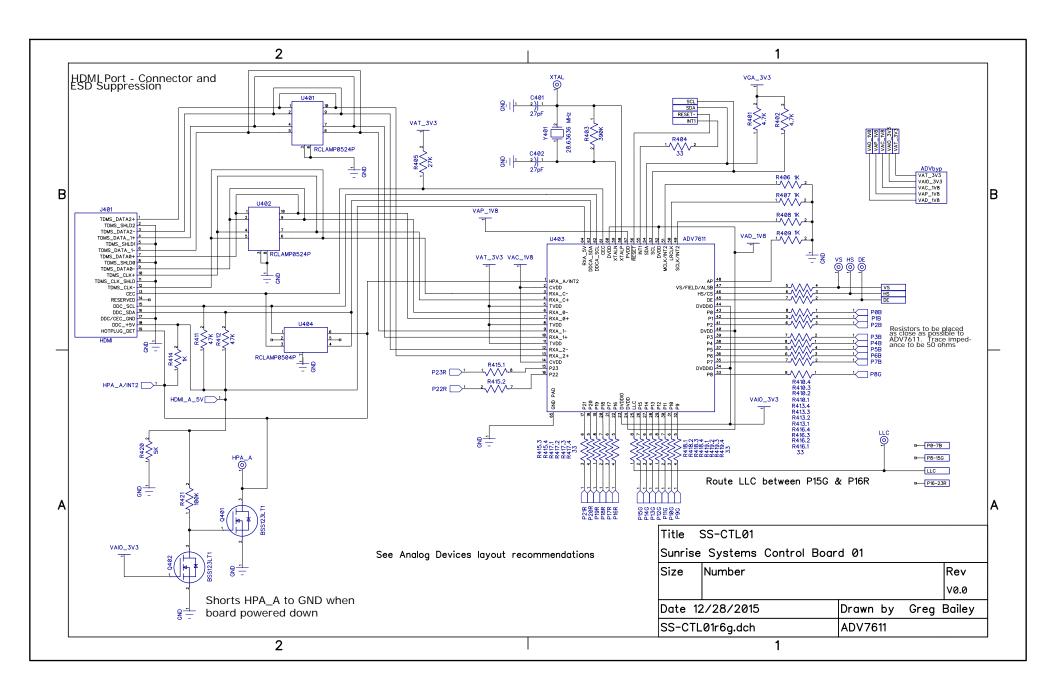

#### 2.1.3 ADV7611 Video Receiver

We have borrowed circuitry recommended by Analog Devices for its ADV7611. This chip is configured, decoupled and powered as recommended by Analog Devices. We configure it to demand 1080p video at 60 Hz with fully standard sync and frame timing.

#### 2.1.3.1 Problems with Analog Devices design

In using the evaluation board from Analog Devices the following problems were observed:

1. HDMI hot plug detection: There is basically no load on the +5V line from the HDMI source. As a result we do not perceive that the cable has been unplugged and the HDMI Hot Plug detect line is left high. We see the LED on the eval board is on, but that LED is powered by the onboard +5V and not by the cable. To alleviate this we have added a 5K resistor to ground from the **DDC\_+5V** line.

#### 2.1.3.2 Procedures

RESET- is asserted for 10 ms after which we wait 10 ms before talking to the chip. After reset, all internal registers are in their default states and the HDMI hot plug detect signal is driven low by the **HPA\_A/INT2** pin. By default settings, this signal will be released to go high 1 second after reset if an HDMI source is plugged in.

When hot plug detect is low, sources are supposed to assume sink is not up and are not supposed to try talking to them. When the hot plug detect signal goes high, a valid EDID 1.3 as defined in CEA-861-D must be available along with a CEA EDID Timing Extension Version 3 that includes an HDMI Vendor Specific Data Block, all per 8.3 in the HDMI spec. We must therefore make our EDID ready to read within 1 second after resetting the chip, whether or not an HDMI cable is plugged in. If we later on change the EDID, we are required to signal the source by driving hot plug detect low for at least 100 ms.

Thus, immediately after ADV7611 reset our critical path actions are to initialize registers as recommended by ADI and then to make the EDID ready to be read. Having done those things within the required time we are free to set the rest of the chip up.

CEC Physical Address Discovery (HDMI 8.7.2) is mandatory even if we are not CEC-capable; we appear to comply by simply putting the default address into the EDID structure.

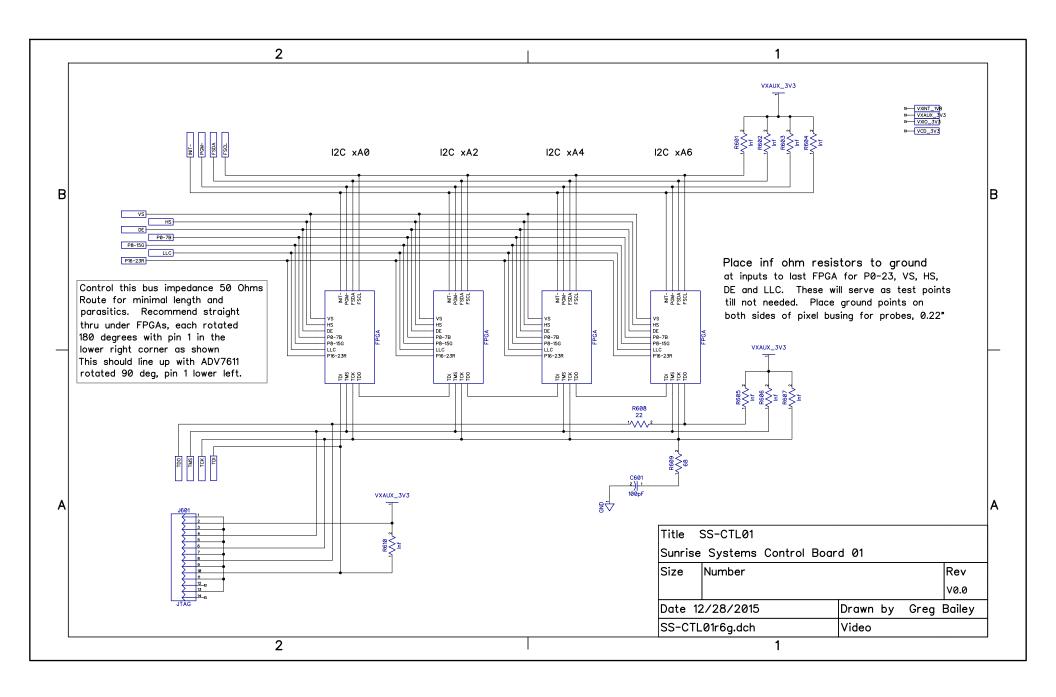

#### 2.1.4 Video Section

This consists of four FPGAs on the pixel bus, with provision for daisy chained JTAG configuration, either by the GA144 or by a Xilinx programmer, and I<sup>2</sup>C communications for managing them later. The I<sup>2</sup>C addresses of the four FPGAs are A0, A2, A4 and A6; this is in order down the bus starting at the ADV7611, in order of the JTAG daisy chain, and in order left to right of the four 15-column segments of the LED display.

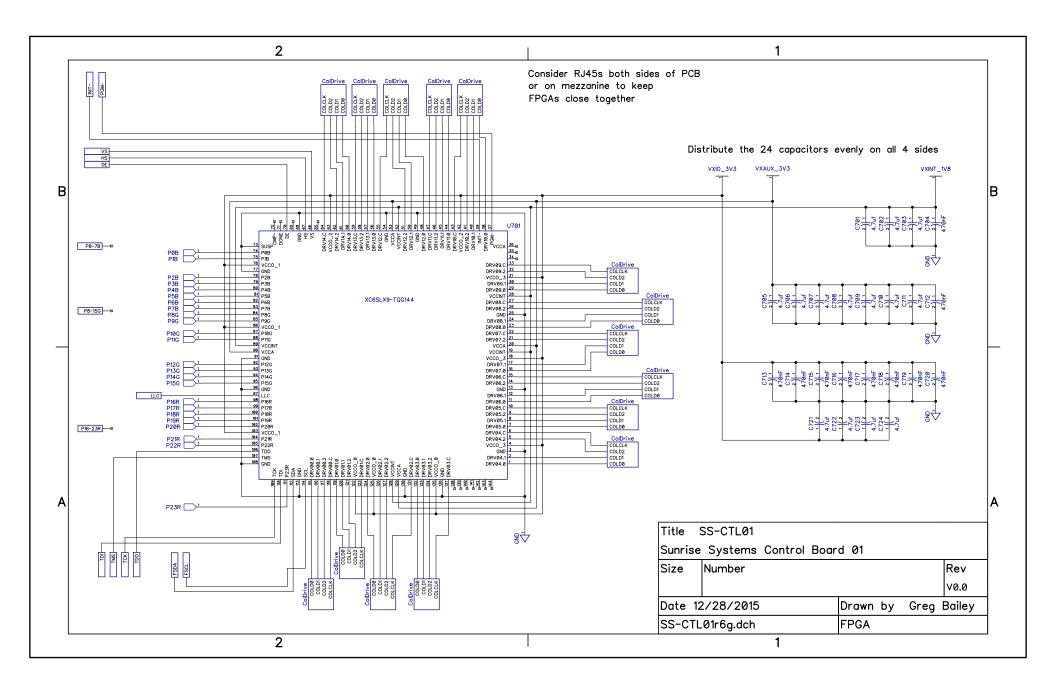

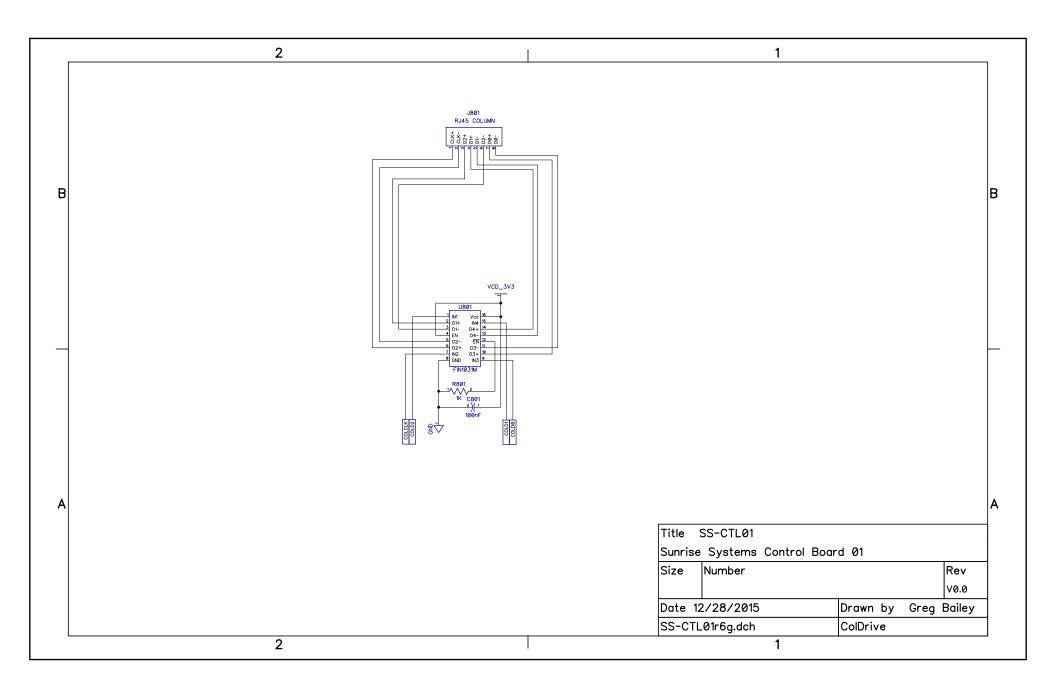

Each FPGA drives 15 columns of modules with 4-bit LVDS cables (we assume Cat5.) For each of these there is a quad LVDS line driver and an RJ45 connector. The FPGA specification is as follows:

#### 2.1.4.1 Lessons Learned from Prototype

The pixel bus (24 bits plus VS, HS, DE and clock LLC) laid out in the way we planned (pixel bus straight across from the ADV7611 through the four FPGAs on the bottom of the board; all crossing signals are routed on the top and middle signal levels) is much cleaner than was the same bus on the Analog Devices evaluation board. With no power to any of the FPGAs, the signals to be sampled on the rising clock edge seem to be firmly in their desired states when the edge comes by, as seen here: Top trace is LLC, bottom is B7 with a transition from 0 to 255 on blue.

#### 2.1.5 FPGA Specification

The problem statement for the FPGA is simple, but timing is critical. The substantial pin-out requirement in combination with Sunrise preference of FPGAs require that four FPGAs be used.

Input to the FPGA is a stream of pixels supplied by the ADV7611 HDMI chip as 24-bit parallel data clocked at 150 MHz by the LLC signal, and qualified by the framing control signals.

#### 2.1.5.1 Framing Awareness

Firstly the FPGA must discriminate between the horizontal and vertical sync delays and the actual delivery of 1920x1080 pixels. No pixels will be processed during those delays; i.e. the FPGA will receive only 1920x1080 LLC events as incoming pixels per frame.

The FPGA must be configurable to isolate a rectangular window, corresponding with the physical display, from each incoming frame. The origin of this window is expressed as WOX and WOY coordinates origined in the upper left corner, which may be zero, and the size as WNX and WNY such that WNX  $\leq$  (1920-WOX) and WNY  $\leq$  (1080-WOY). WNX must be divisible by PX so that the window width is an integer number of module widths in pixels. Later on we added registers for origin and width of each column so that columns of differing widths could be used to build a sign.

The first W0Y lines of each image (if W0Y nonzero) will be ignored and the following WNY lines processed in each frame. For each processed line, the first W0X pixels (if W0X nonzero) will be ignored and the following WNX pixels processed in each frame.

#### 2.1.5.2 Pixel Processing

Each of the first PX pixels in the active window of each scan line will be inserted into a FIFO for transmission to column zero modules. The next PX pixels will be inserted into a FIFO for transmission to column 1, and so on for MX FIFOs. We believe that the limit for MX is 60 in any practical configuration, so there will be 15 FIFOs in each FPGA (for maximum MX of 60) and each will have a depth of 40 pixels (the maximum PX).

The output side of each FIFO, as soon as it is not empty, will feed a serializer that transmits each pixel as seven (21-bit) or eight (24-bit) parallel words of three data bits, using straight DC level coding, and a half-frequency clock. Setup time is provided by the GA144s, so all four lines should be driven with no skew. These four signals must be 3.3V single ended CMOS (push-pull) logic.

The clock for outbound 3-bit words must be derived from LLC but will be divided down by a factor of MX (MX\*2 given that it is a half frequency clock.) Note that this means each of the FIFOs will be sending data down its column as soon as the first pixel is in the FIFO, and throughout the remainder of the current scan line, the next horizontal blanking interval, and into the next scan line a variable distance depending on which column it is, so that the FIFO is emptied before the first pixel for that column in the next line is added to the FIFO. Because transmission down a column continues well into the next scan line, this would lead to complications if LLC is only driven during the active part of each frame; however, that is not a problem with the ADV7611 whose LLC is continuous.

#### 2.1.5.3 Configuration Control

The key parameters that will vary by installation are WOX, WOY, WNX, WNY and NX. Initially we thought these would be loaded via JTAG, but we later decided to use I<sup>2</sup>C so parameter changes wouldn't require re-programming the FPGAs.

#### 2.1.5.4 Possible Complications

Although we initially assumed that any display would be built as an array of identical modules, it soon became apparent that to meet customer requirements for particular sign sizes there was a good chance that different modules may be used on the bottom or right-hand edges, for example, so the FPGAs gained more configuration registers.

#### 2.1.5.5 Clarifications to the FPGA Specification

The clock used for transmitting 3-bit values down a column from its FIFO will be derived from the pixel clock using a fixed integer divisor; if a single divisor value is needed it will be 6 (correct for 48 columns), giving 25 megatriads per second (40 ns period) and a square wave clock frequency of 12.5 MHz. When a FIFO has been emptied, the clock output will stop generating transitions but will remain in the same state (high or low) as it was after the edge clocking the last triad sent. The edge for clocking the first triad of the next line will begin at this state. There will be no discontinuity in this clock signal across frame boundaries and there will be no spurious edges sent; each edge sent will clock three bits of data that will be taken seriously.

The FIFOs will be filled, and emptied, only for the 1080 active rows of a 1080p display. Silent clock line is used by the VMODs to detect end and start of frame.

#### 2.1.5.6 I<sup>2</sup>C Registers and Functions

The four FPGA chips 0..3 are addressed as I2C devices xA0, xA2, xA4, and xA6 respectively. Within each FPGA the registers are assigned as follow:

| Address | Bytes | R/W | Default    | Significance                                                                               |

|---------|-------|-----|------------|--------------------------------------------------------------------------------------------|

| x00     | 2     | RO  | x5501      | ID code                                                                                    |

| x01     | 2     | RO  | (s/b 2200) | Current pixels per HSYNC line                                                              |

| x40+n   | 2     | RW  | 40         | Column $\boldsymbol{n}$ width in pixels [140] $\boldsymbol{n}$ in [015] (PX <sub>n</sub> ) |

| x80+n   | 2     | RW  | 40n        | Column $\boldsymbol{n}$ pixel origin [01919] $\boldsymbol{n}$ in [015] (W0X <sub>n</sub> ) |

| xC0     | 2     | RW  | 0          | Top row of sample window [01079] (WOY)                                                     |

#### 2.1.6 Roadmap

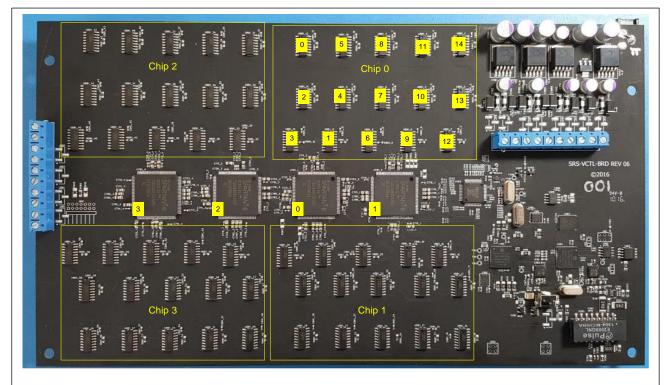

The layout of FPGAs and associated RJs on the back of the board is not quite sequential. Here's the top side:

Top side of VCTL PCB - Each chip's columns same order, RJs on bottom same pattern as drivers on top

The sequence of FPGA numbers above reflects their sequence in the TDI-TDO daisy chain. Recommend no change in the planned SPI addressing for the FPGAs; the connector grouping is rational enough as it is and 0/1 were intended to feed the leftmost columns as the layout supports. We may wish to rename the pins on the FPGA so that the numbering of connectors in each group of 15 is more rational; one simple fix would be to renumber columns 0, 1, 2, 3 so that they fit the pattern of the remaining columns 4..14. Once this has been determined we can come up with a reasonable silkscreen for the backside of the PCB.

#### 2.1.7 ADV7611 Observations

```

After power-up:

300 LOAD ok

+ADCHIP ok

. AD

Chip 2051 HDMI 5V NO. Assert HPA NO. TDMS clk detect NO.

TDMS PLL locked NO. VS Lock NO. DE Lock NO. HDMI PLL Lock NO.

STDI laced NO. CP proc lace NO. Lace conflicts YES.

HDMI section mode DVI HS, VS high 00 X=0 Y=0

Bits/gun=8 Interlaced NO. FIFO locked NO.

Line wid 1 Front 0 HS 1 Back 0

Fld hght 0 Front 1 VS 0 Back 8191

TDMS 0 kHz. Input colors 0 (0=RGB, 1=full)

CP section CSC BYPASS. STDI valid NO. Lines/frm=0

Laced NO. Xtal/8Lin=16383 Vsync=0 Xtal/fld=0

CP Free-running w/mode&std. CP Free-running: YES.

INT1 NO. STDI valid NO.

io/42 3 CP Unlocked

io/47 6 Undefined

io/5B 2 CP input has changed from locked to unlocked

io/65 6 Audio is muted ok

After plugging into Win7 notebook bat and sending video (identify):

. AD

Chip 2051 HDMI 5V YES. Assert HPA YES. TDMS clk detect YES.

TDMS PLL locked YES. VS Lock YES. DE Lock YES. HDMI PLL Lock YES.

STDI laced NO. CP proc lace NO. Lace conflicts YES.

HDMI section mode DVI HS,VS high 11 X=1920 Y=1080

Bits/gun=8 Interlaced NO. FIFO locked YES.

Line wid 2200 Front 88 HS 44 Back 148

Fld hght 1125 Front 4 VS 5 Back 36

TDMS 148484 kHz. Input colors 0 (0=RGB, 1=full)

CP section CSC BYPASS. STDI valid YES. Lines/frm=1124

Laced NO. Xtal/8Lin=3385 Vsync=5 Xtal/fld=1864

CP Free-run buff locked. CP Free-running: NO.

INT1 NO. STDI valid YES.

io/42 2 CP Locked

io/42 4 STDI Data Valid

io/47 6 Undefined

io/5B 1 STDI Data is valid for sync channel 1

io/5B 3 CP input has changed from unlocked to locked

io/65 6 Audio is muted

io/6A 0 DE Regeneration is locked to incoming DE signal

io/6A 1 VS Filter has locked and vertical sync params are valid

io/6A 4 TDMS Clock is detected

io/6A 6 TDMS PLL is locked to incoming clock

io/6F 0 HDMI cable +5V is detected

io/83 1 TDMS Freq has changed by more than FREQTOLERANCE

io/83 6 Irregular or missing pulses have been detected in TDMS clock ok

```

# 2.2 Production VCTL PCB

FTDI FT232R chips need to be configured. Do the normal sequence of actions in the PCBCOM document with differences: In place of step 5, change two string descriptors:

- Product Description is Sunrise VCTL Port A (and B)

- Serial Number is GAVCTLnnnA (and B) with first chip 001. ("Device Instance Path")

#### 2.2.1 Notes for Production Board

- Add LEDs to show status. This board has no visible indications of its condition without hookup to serial or network.

- The new SPI flashes (without reset lines) require that we put a 1k pull-up resistor on GA144 zero 705.3 going to **CE** line on the flash, so that we can boot again after GA144 reset.

#### 2.3 VCTL Test & Commission

To manufacture the VCTL in production, procedures and jigs for testing and commissioning will be required.

#### 2.4 Module PCB

Because this board will be produced in volume, we must minimize cost of manufacture. The prototyping board is necessarily larger and more costly than the production target because we must be able to experiment with changes in the critical parts, particularly line drive and receive, reset and watchdog circuits, as well as final bit assignment in parallel ports for optimal code. The flash is only used for booting and nonvolatile configuration data; its size may be reduced if it will save cost. In this section we walk through the prototype schematic.

#### **Lessons Learned from Prototype:**

The power consumption of this board, while small, is considerable when multiplied by 30 or so for the number of modules in a column. Power daisy chaining must be considered carefully as to board connection method.

The massive power spike when the board is first reset after power-up (on the order of 250 to 300 mA per board) is probably going to be intolerable. This spike is due to having all of node 007 unused parallel input pins connected together and grounded through a pull-down resistor. Until we are able to get to node 7, change outputs to all ground (for no spike next reset), and switch the node to input mode, the drivers are all shorted together with indeterminate values. The alternatives are to put 14 separate pull-downs on the unused pins (cleaner design, higher cost) or leave them open (which has the potential for bringing metastable voltages into the ALU) and spend additional time and resources masking the value off in the input path.

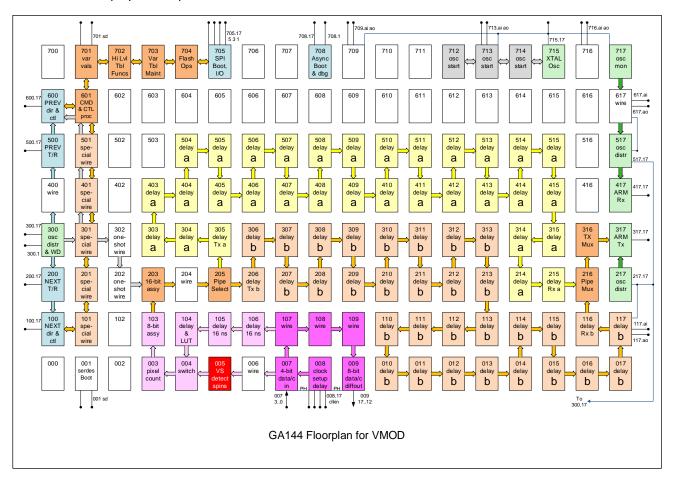

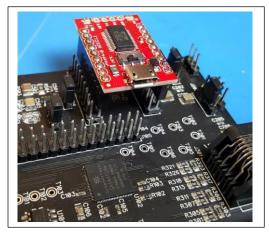

### 2.4.1 GA144 Page

This page covers the GA144, its decoupling caps, and SPI boot flash; in normal mode, the boot flash is enabled.

For prototype only, there are hole patterns (not populated with headers) serving as test points for the boot flash, and patterns for selecting which GPIO pins are used for other functions (crystal, serial to and from LED module, serial to and from neighbor modules for control/status/configuration interface). There's no pattern for crystal itself because that will just be soldered down to holes in the patterns J4 and j5 for now (actually plugged into header pins.)

To interactively program this board we'll use a SparkFun FTDI module plugged into the J102/J103 patterns, in conjunction with no-boot jumper J101 for flash and the FTDI reset enable jumper J108. We are suggesting that production testing (and, if necessary, flash programming) will be best done using a bed of nails that will contact exposed pads for IDE serial on the bottom side of the board, along with pads for the no-boot function, to minimize manufacturing cost of these boards.

Test points are provided for video clock+ out, and clock and bit 0 inputs, on the pixel pipeline at the GA144.

#### 2.4.1.1 Lessons Learned from Prototype

Low voltage testing with IDE fails at about 1.62V; suspect it is the FTDI chip that fails us here. Will have to do low V testing after we have an array of boards running without assistance.

The newer SPI flash chips do not have a reset line as such. It appears we have to allow chip select to go high in order to reset that sort of chip. We will have to put a pull-up resistor on the chip select line on the production board.

The flash is active for about 18.4ms after reset is released, with only half the RAM in every node being loaded with ganglia. The actual time used will probably be on the order of twice that by the time the whole application is being loaded, and longer still with the lower speed flashes.

The time required for ameliorating the shorts on node 007 outputs, the first time the VMOD is powered up, is about 1ms after rise of the reset signal. This will probably be slower with the lower speed flashes. As it turned out it was moot because the parallel port shorts dragged supply voltage down too low for the flash to work at all.

#### 2.4.2 Power Page

Incoming 1.8 and 3.3V supplies are decoupled and provision is made for power measurement. All six headers on this section should be populated with male pins. Test points are provided for supply buses.

#### 2.4.2.1 Lessons Learned from Prototype

We screwed up with the power inputs. Rather than two separate 1x3 headers we should have used a single 2x5, reducing chances of error and increasing sturdiness of connection.

The production boards are going to need a very good way of connecting their power.

#### **Power Budget**

An idle chip, not driving differential video output but with parallel port set correctly, burns about 5 mA. When the video bus drivers are turned on (driving differentially), the terminations burn another 25 to 28 mA.

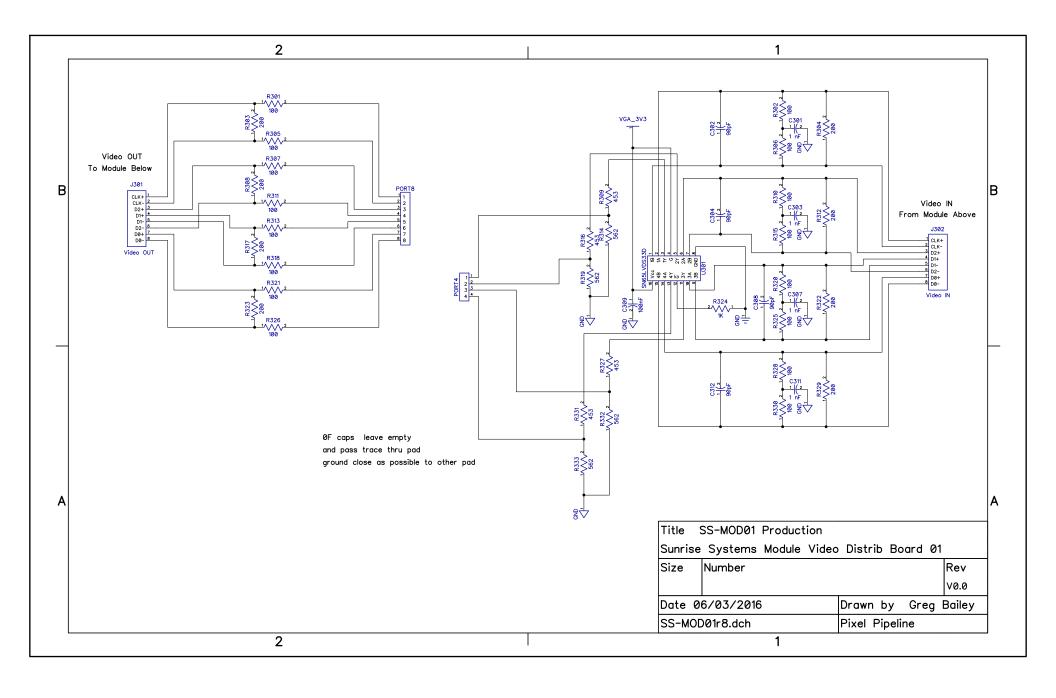

#### 2.4.3 Pixel Pipeline Page

Eight lines from pins on node 009 (Port8) drive the cat5 cable through the resistor network Warren designed. An RJ45 connector is used for this connection although in production it may be best to omit the connectors. The incoming video is connected by an RJ48 to another of Warren's networks feeding an LVDS receiver which is then connected to four pins of node 007 and pin 008.17 (for clock only) of the GA144 using voltage dividers to step down from 3.3V to 1.8V. In production this might be simplified to series current limiting resistors only. Provision is made for caps in case there's incoming noise to suppress, and for differential probing of data line 0 at the input to the LVDS receiver chip. Preliminary work with these networks and 2 feet of Cat5e cable indicates there will be about 700 mV peak to peak on the incoming differential receiver pins with good, crisp rail to rail signals and only a little ringing.

The four signals on the pixel daisy chain, with their cable pin-out and GA144 connections, are as follow:

| Cianal | GA14 | 4 Pins | RJ45 pins |   | GA144  | Second |

|--------|------|--------|-----------|---|--------|--------|

| Signal | Tx+  | Tx-    | +         | 1 | Rx pin | Rx pin |

| Clk/2  | A10  | A11    | 1         | 2 | D03    |        |

| Bit 2  | A12  | A13    | 3         | 6 | D00    |        |

| Bit 1  | A14  | A15    | 4         | 5 | D01    |        |

| Bit 0  | A16  | A17    | 7         | 8 | D02    | 008.17 |

Having determined that the GA144 will need to do table lookup both for interpreting incoming data and for generating outgoing differential signals, the above arbitrary bit assignments have no effect on code design.

#### 2.4.3.1 Lessons Learned from Prototype

Each transmit pair uses negligible current when both pins driven same, but on the order of 6 mA when driven differentially due to the load resistors. It looks like 25-28mA per module for this alone.

The  $10k\Omega$  voltage divider stepping the 3.3V outputs of the receiver chips down to 1.8V was a mistake, rolling off the incoming signals too far to be useful. Rescaling it to a 1k divider gives much more usable signals.

The incoming signal on D0 with 90pF parallel cap is considerably cleaned up relative to the other three lines. It may be worth treating the other three lines the same way.

A common mode observation: At one point the VCTL was powered on an old ball and tube ungrounded 110VAC circuit that shares its common with a second circuit, while the VMODs were powered by a new circuit that had a solid ground. The measured voltage between ground on the second circuit and the ground lug of the power supplies for the VCTL was on the order of 12VDC and 67VAC. Video was nevertheless working, most of the time, although periodically a horizontal band of grizzling noise would appear and "roll" down two of the columns. This would seem to imply pretty good common mode rejection on the quad line receivers we chose!

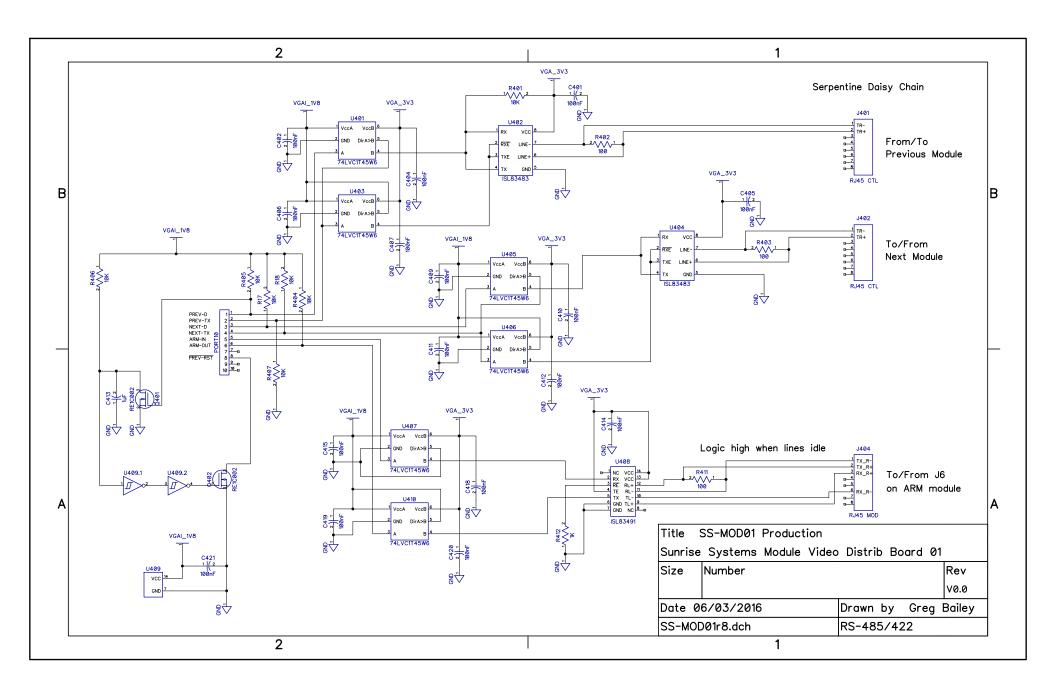

#### 2.4.4 RS-485/422 (4)

This sheet has RS485 transceivers for the control/status daisy chain (max 250 kbit/s), RS422 transmitter and receiver for talking with the Sunrise LED module, and level shifters for all those. 3.3V transceivers are used because this gives better common mode capability; those with 3.3V differential sides and 1.8V logic sides are more expensive than is the combination of 3.3V-only parts with a level shifter. RJ45s are used for these interfaces although in production these connectors will probably be omitted.

#### 2.4.4.1 Control/Status Daisy Chain

Note! The simplest/cheapest way we see to manage the control channel is a single serpentine daisy chain fed by a single RS485 interface on the Control Board, leading to the top of the left most column (column zero) of modules. The daisy chain proceeds, with half duplex single-pair RS485 connections, down that column with each module's "next" line connected to the "previous" input of the next lower module. From the bottom most module of column zero, its "next" line connects to the "previous" line of the bottom module in column 1. The daisy chain proceeds upward from there with each module's "next" line connected to the "previous" line of the next upper module. At the top of column 1, that module's "next" feeds the "previous" line of the top module in column 2, and so on.

This requires wiring odd and even numbered column distribution assemblies differently. There might be other ways but that would imply different code in modules destined for odd or even columns, with different floor planning problems, or else jumpering or other trace routing options to configure a board for odd or even columns. We think the wiring is the lesser of evils, but the trace routing option would work equally well without software change... although once assembled the odd and even cable assemblies would still not be interchangeable, and if the trace routing option was destructive the PCBs themselves would not be, either.

With the serpentine method, reset can be propagated through the daisy chain for sign power-up, and it is possible to plan for selective reset of a given module. Sequential serpentine module addresses become known to each module during power-up and can be stored in flash. Once all modules have unique addresses, each can be informed of its configuration parameters including position in column, dimensions of associated LED module, and so on, all of which is known to the control processor.

This page includes a serpentine reset circuit that allows the previous module in the control/status daisy chain to reset us by holding its signal in the physical low state (same state as start bit but for a very long time like a BREAK signal). When this line is in input mode it is monitored for a reset signal. RC network R406 (10k) and C413 (1 uf) accumulates charge with a 10 ms time constant. Whenever the signal line from previous module goes physical high (stop bit, idle), this charge is shorted to ground through an N transistor. When the charge is allowed to build to normal  $V_{IH}$  for 1.8V CMOS parts, something on the order of 7 ms, a low signal is sent to the main reset circuit. We will probably be running at least on the order of 9600 baud so this should be safe. The time constants of all modules are additive for resetting the whole sign; 2000 times 7 ms is already 14 seconds, so this could get out of hand in a hurry.

Test points are provided for differential probing of the data lines from the previous module PCB. Jumper J403 provides for disabling the daisy chain reset.

The RS485 transceiver circuitry is presently wired such that rest state is high on the single-ended lines, consistent with the fail-safe mode of the receivers. TR+ (pin 2) of the connectors is high and TR- low in rest state. On the module boards, the data lines for all outputs are pulled weakly high (10K) to overcome the weak pull-downs (40K) when the GA144 is in reset; and the direction lines for the transceivers are weakly pulled down to ensure input mode on both sides of the daisy chain. Data lines on the control board are pulled up as well. Thus the states of all the lines are high when the GA144 is in reset, when the lines are idle, and when a cable is open or unplugged. Note that this is the opposite polarity as normally used for GA144 serial I/O.

The RS485 line from the previous module is in input mode at reset and will be in input mode at all other times except when we are transmitting to the previous module. Thus, normally we can be reset by the preceding module. Warning: If a module ever sticks in output mode on its line to the preceding module, the stuck module may no longer be reset by the daisy chain until it becomes un-stuck or power is cycled.

#### 2.4.4.1.1 Lessons Learned from Prototype

The ISL83483 does not seem to have a normal high failsafe on open input, at least not reliably; same type of behavior as noted below for the ARM interface. This means that loss of input connection could put us in reset.

It also means that we cannot depend on the fail-safe mode to prevent the next module from resetting while the current module does. Pull-ups should be added to both the data and direction lines (Port10.3 and 4 respectively) and the pull-down on Port10.4 removed so that we drive control to the next module high while in reset.

Observed rise time of C413 is about 7.45ms ground to 0.9V and the time to actual RSTin assertion is about 7.85ms. These timings are consistent with the 10ms TC of the circuit. Fall time from 1.8V to ground is about 5µs so as long as a bit time is greater than that, and as long as character frame time is considerably less than 7.5ms, this set of values will work well. For a faster serpentine reset, run at a high bit rate, shorten the time constant and use precision R406 and C413 to minimize TC variability.

#### 2.4.4.2 RS485 4-wire ARM Interface

Communications to and from the ARM on the Sunrise module use two wire pairs, connecting to J6 on the Sunrise module. Pins 1 and 2 are TX-R- and TX\_R+ respectively, signals from the ARM. Pins 3 and 6 are RX\_R+ and RX\_R-respectively, signals to the ARM. Polarities are as above, with the single logic lines high, and the + side of a pair higher than -, when the line is at rest (stop bit state). A weak pull-up resistor is used to maintain the single ended output line high when the GA144 is reset. Test points are provided for differential probing of the data coming from the ARM.

#### 2.4.4.2.1 Lessons Learned from Prototype

The ISL83491 does not seem to have a normal high-failsafe on open inputs even though the data sheet says it does! Measuring 0.228V on pin 12 and 0.227V on pin 11 I see pin 2, the RX pin, is low! Boards 002 and 003 both behave this way. Added a 1k pull-up to pin 2 and still it is 0.03V so it's sure enough being driven.

#### 2.4.5 WatchDog Timer (5)

The main reset circuit is also on this sheet. Reset is triggered by power-up, by a reset button on the prototype board only, by the reset signal received from the upstream control/status module as above, or, during development, by the FTDI reset signal; this is done using a commercial reset IC. In addition there is a watchdog circuit in this section, using a commercial chip set at nominally 1.6 seconds.

The reset circuit pulls **RST-** to ground as soon as its input signal **RSTin** is high enough to turn its output N transistor on, at about 0.70V. It releases **RST-** which rises with a TC of 110µs when the **RSTin** signal rises above 1.6V.

**RSTin** may be grounded by a reset button, by a signal from the FTDI serial dongle (if enabled by J108), by the watchdog circuit (if enabled by J501), or by BREAK on the incoming control channel (if enabled by J403). Each of these reset sources pulls **RSTin** down very quickly, and holds it down for a varying amount of time. The reset circuit does not assert **RST-** low while **RSTin** is at ground. It only does so when the **RSTin** line is released, at which time it rises with a TC of 10.1ms, producing assertion of **RST-** for about 12.5ms. This should be long enough to allow an SPI flash to complete an erase operation; if not, it can be extended to about 25.4ms by removing R409 from the circuit. *However, for reasons not yet understood, the actual duration of the RST- signal is only about 2.6ms.*

Jumper J502 2-3 sets normal mode in which the watchdog circuit is enabled whenever **RST-** is high; 1-2 allows software to control it, but we do not plan to test this mode unless required, because it weakens the whole concept. J501 is inserted to empower the watchdog circuit to reset the PCB, and it will do so unless there is a rising or falling edge on the **WDIN** net within 1.6s [1.12..2.24s] of end reset, or since the last such edge, at which it asserts **RSTin** low for 210ms [140..280ms]. Empirically, a chip that has not been programmed will, with the default jumpers, reset itself roughly every 1.75s. During testing, either straight IDE or with serial boot stream, J502 must be moved from 2-3 (normal) to 1-2 (disable).

#### 2.4.5.1 Commissioning a prototype VMOD board:

- 1. Dismantle switch on Sparkfun FTDI dongle so that it will use the **VCCIO** we provide, and solder two 9-pin female headers to its underside. Follow procedures in PCBCOM document except that Product Description is VMOD Serial Dongle and Serial Number is GAVMODBOBNN with first chip 01.

- 2. Solder 10k resistor between VGAI\_1V8 and the RST- net, required by change to open drain reset chip.

- 3. Solder all missing headers to board except J503 and J504. Add ground rail between J106 and J107.

- 4. Add default jumper blocks before testing:

| Block | Pins | Effect                        | Comment                       |

|-------|------|-------------------------------|-------------------------------|

| J201  | 2-3  | Enable 1.8V to Core           | Center pins                   |

| J202  | 2-3  | Enable 1.8V to I/O            | Center pins                   |

| J203  | 2-3  | Enable 3.3V to I/O            | Center pins                   |

| J108  | IN   | Enable <b>RSTin</b> from FTDI | Note shortens reset pulse 10x |

| J502  | 1-2  | Disable Watchdog              | Toward center of board        |

| J501  | IN   | Enable Watchdog Reset         | Underneath board              |

| J101  | IN   | No Boot                       |                               |

| J403  | 1-2  | Disable Control Reset         | Away from ground headers      |

#### 5. After testing install the following:

| GA144 Pin   | J105 | J104 | Signal               | Comment                   |

|-------------|------|------|----------------------|---------------------------|

| 600.17      | 1    | 2    | PREV Tx Enable       |                           |

| 500.17      | 2    | 1    | PREV Data            |                           |

| 300.17      | 3    |      | XTAL monitor net     | Wire Wrap to J105.7       |

| 300.1       | 4    | 15   | WDIN Watchdog Toggle | 3" (Yellow) jumper        |

| 200.17      | 5    | 3    | NEXT Data            |                           |

| 100.17      | 6    | 4    | NEXT Tx Enable       |                           |

| 217.17      | 7    |      | XTAL monitor net     | Wire Wrap to J105.3,10    |

| 317.17      | 8    | 6    | Data out to ARM      |                           |

| 417.17      | 9    | 5    | Data in from ARM     |                           |

| 517.17      | 10   |      | XTAL monitor net     | Wire Wrap from J105.7     |

| 708.17      | 11   | 8    | FTDI Data In         |                           |

| 708.1       | 12   | 9    | FTDI Data Out        |                           |

| 715.17      | 13   | 14   | XTAL                 | Mounted on 2x2 hdr        |

| <ewd></ewd> | 20   | 16   | EWD no GA144 control | Wire Wrap always disabled |

#### 6. Change jumpers for normal operation from boot flash:

| Block | Pins | Effect               | Comment                                                                               |

|-------|------|----------------------|---------------------------------------------------------------------------------------|

| J502  | 2-3  | Disable Watchdog     | Toward edge of board                                                                  |

| J101  | OUT  | Flash Boot           |                                                                                       |

| J403  | 2-3  | Enable Control Reset | Toward ground headers; do NOT do this if there's nothing driving our RS485 IN socket. |

If you insert J101 to disable flash boot, you must also move J502 back to pins 1-2 because nothing will be keeping the watchdog happy.

#### **2.4.5.2** Development Procedures:

- **Disable Watchdog to use straight IDE or serial stream boot**, by moving J502 jumper from 1-2 (toward center of board) to 2-3 (toward edge of board). Once serial stream boot is finished you can move the jumper back, but doing so can lead to confusion so it is not recommended:

- **Don't enable watchdog when booting from serial stream**; if the watchdog trips this reset won't reboot if the No Boot jumper is still in.

- **Insert "No Boot" jumper J101 when using straight IDE to generally access the chip.** This will require disabling watchdog as noted above.

Note that IDE talk does a reset. To use the IDE in some combinations such as with flash enabled it may be necessary to say reset after talk before anything will work.

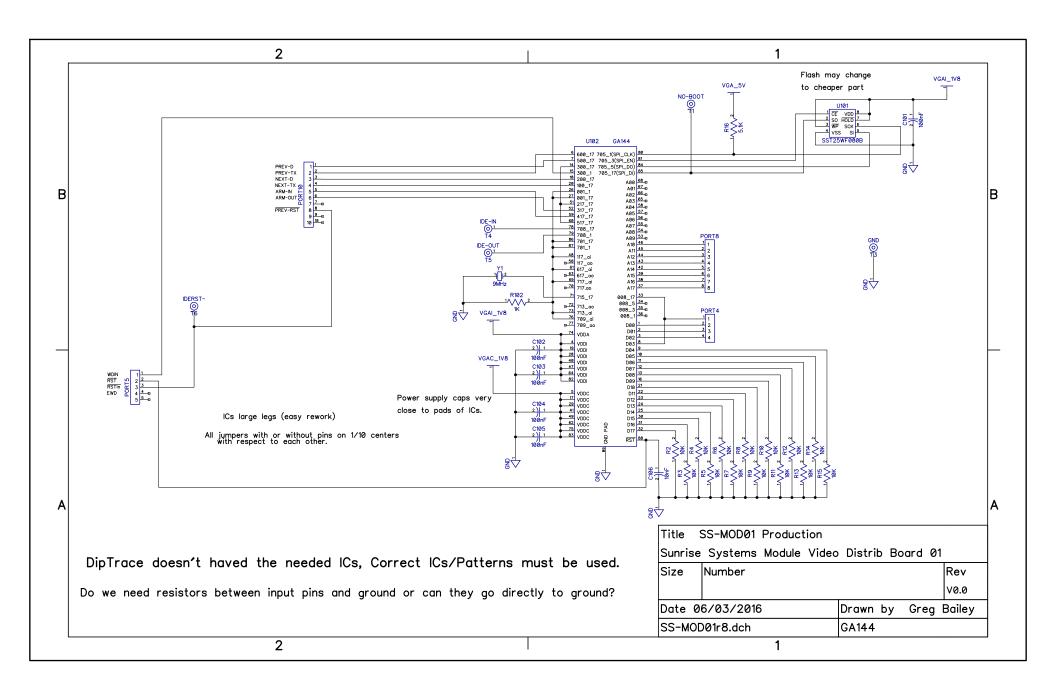

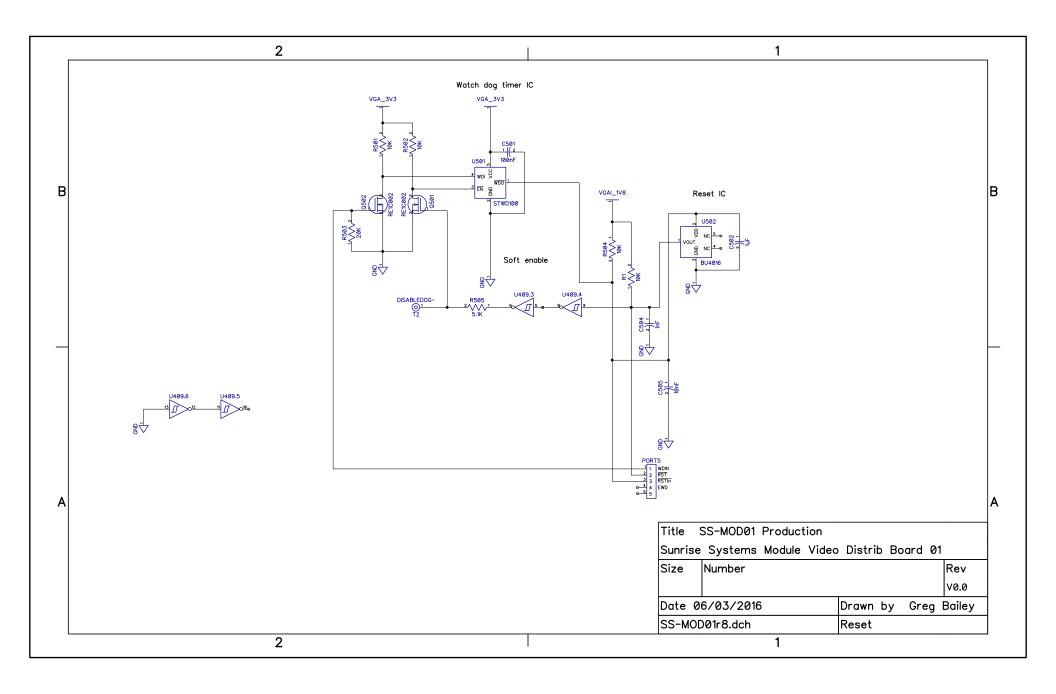

#### 2.5 Production VMOD PCB

Changes for production began with the file SS-MOD01r6.dch received from Sunrise and dated 1/07/16 16:44. We have renamed this file SS-MOD01r7.dch because we actually delivered one in December called r6. This section documents each change we made to this r7 file in generating r8.

Note to Sunrise: We are not using the same DipTrace libraries Matt did. If a BOM change required changing a library part we have done so and the need to maintain Matt's library is indicated along with the change. Our libraries are part of the delivered package but there's no way we know of to reconcile ours with Matt's other than making the parallel changes manually on his.

In updating the BOM we have used a "code": Resistors and caps shown as 10% can be whatever precisions are handy for you, whereas those shown with tighter tolerances have values used to set time constants, signal amplitudes or proper terminations and should be as close to what we write as practical. We have reduced all discrete SMT components to the smallest footprints allowed by the values or power dissipations as appropriate. We have assumed that 0402 is the smallest you'd like to be picking and placing; if you actually want to mess with 0201 some but not all of the parts can be that small.

Please note that in producing BOM ordering by name and value, DipTrace combines tolerances. It's necessary to unravel the BOM by part to see the tolerances. This may or may not matter depending on how you choose to treat tolerances in manufacture.

We have not gone to the length of selecting smaller packages for the ICs on this PCB. If you wish to adopt smaller package sizes that is fine with us although given no test points it would be nice to stick with parts it's feasible to probe. Leadless packages have obvious disadvantages if anything needs to be measured or investigated.

The first set of changes reflects differences between r7 and the prototype boards as built:

- 1. Change U502 from BU4916 (reset chip with push-pull outputs) to BU4816 (open drain). The latter are much more readily available than are the former. *Library change (define BU4816)*.

- 2. Change U101 from SST25WF080 to 080B, validated on several of the prototype VMOD boards. *Library change* (define 080B and its part number.)

- 3. Note that all the 74LVC1T45W6 parts were replaced on prototype with TI SN74LVC1T45DBVR due to availability issues. This substitution seemed to work fine. We have not changed the schematic or BOM to reflect this.

The second set pertain to changes we have made to the prototype boards as built to yield a working sign:

- 4. Add pull-up resistor R1 on VOUT of U502, 10k 1% 0402.

- 5. Change R309, R316, R327, R331 from 5.11k to  $453\Omega$  1% 0603, to correct divider (3v across this).

- 6. Change R314, R319, R332, R333 from 5.62k to  $562\Omega$  1% 0402, to correct divider (3v across this).

The third set pertains to conclusions drawn during test and debug: